# Dual General Purpose Transistor

The NST3906DXV6T1 device is a spin-off of our popular SOT-23/SOT-323 three-leaded device. It is designed for general purpose amplifier applications and is housed in the SOT-563 six-leaded surface mount package. By putting two discrete devices in one package, this device is ideal for low-power surface mount applications where board space is at a premium.

- h<sub>FE</sub>, 100-300

- Low  $V_{CE(sat)}$ ,  $\leq 0.4 \text{ V}$

- Simplifies Circuit Design

- Reduces Board Space

- Reduces Component Count

- Lead-Free Solder Plating

#### MAXIMUM RATINGS

| Rating                         | Symbol           | Value                 | Unit |

|--------------------------------|------------------|-----------------------|------|

| Collector - Emitter Voltage    | V <sub>CEO</sub> | -40                   | Vdc  |

| Collector - Base Voltage       | V <sub>CBO</sub> | -40                   | Vdc  |

| Emitter - Base Voltage         | V <sub>EBO</sub> | -5.0                  | Vdc  |

| Collector Current - Continuous | Ι <sub>C</sub>   | -200                  | mAdc |

| Electrostatic Discharge        | ESD              | HBM>16000,<br>MM>2000 | V    |

#### THERMAL CHARACTERISTICS

| Characteristic<br>(One Junction Heate     | ed)                   | Symbol                             | Мах                                | Unit        |

|-------------------------------------------|-----------------------|------------------------------------|------------------------------------|-------------|

| Total Device Dissipation                  | T <sub>A</sub> = 25°C | PD                                 | 357                                | mW          |

| Derate above 25°C                         |                       |                                    | (Note 1)<br>2.9<br>(Note 1)        | mW/°C       |

| Thermal Resistance<br>Junction-to-Ambient |                       | $R_{\thetaJA}$                     | 350<br>(Note 1)                    | °C/W        |

| Characteristic                            |                       |                                    |                                    |             |

| (Both Junctions Heat                      | ted)                  | Symbol                             | Max                                | Unit        |

| Total Dovice Dissipation                  | _                     |                                    |                                    |             |

| Total Device Dissipation                  | $T_A = 25^{\circ}C$   | PD                                 | 500<br>(Note 1)                    | mW          |

| Derate above 25°C                         | T <sub>A</sub> = 25°C | PD                                 | 500<br>(Note 1)<br>4.0<br>(Note 1) | mW<br>mW/°C |

|                                           | T <sub>A</sub> = 25°C | P <sub>D</sub><br>R <sub>θJA</sub> | (Note 1)<br>4.0                    |             |

| Derate above 25°C                         | T <sub>A</sub> = 25°C |                                    | (Note 1)<br>4.0<br>(Note 1)<br>250 | mW/°C       |

1. FR-4 @ Minimum Pad

# **ON Semiconductor®**

#### http://onsemi.com

NST3906DXV6T1

CASE 463A PLASTIC

#### MARKING DIAGRAM

A2 = Specific Device Code D = Date Code

#### **ORDERING INFORMATION**

| Device        | Package | Shipping                       |

|---------------|---------|--------------------------------|

| NST3906DXV6T1 | SOT-563 | 4 mm pitch<br>4000/Tape & Reel |

| NST3906DXV6T5 | SOT-563 | 2 mm pitch<br>8000/Tape & Reel |

© Semiconductor Components Industries, LLC, 2003 March, 2003 - Rev. 0

#### **ELECTRICAL CHARACTERISTICS** ( $T_A = 25^{\circ}C$ unless otherwise noted)

| Characteristic                                 | Symbol               | Min  | Max | Unit |

|------------------------------------------------|----------------------|------|-----|------|

| OFF CHARACTERISTICS                            |                      |      |     |      |

| Collector - Emitter Breakdown Voltage (Note 2) | V <sub>(BR)CEO</sub> | -40  | -   | Vdc  |

| Collector - Base Breakdown Voltage             | V <sub>(BR)CBO</sub> | -40  | -   | Vdc  |

| Emitter - Base Breakdown Voltage               | V <sub>(BR)EBO</sub> | -5.0 | -   | Vdc  |

| Base Cutoff Current                            | I <sub>BL</sub>      | -    | -50 | nAdc |

| Collector Cutoff Current                       | I <sub>CEX</sub>     | -    | -50 | nAdc |

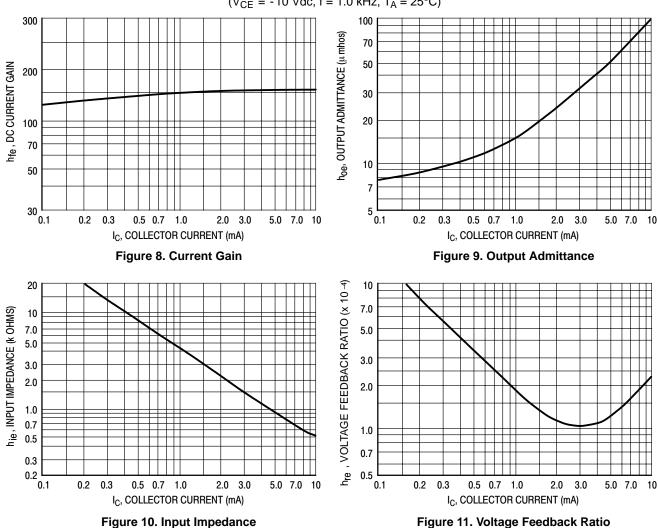

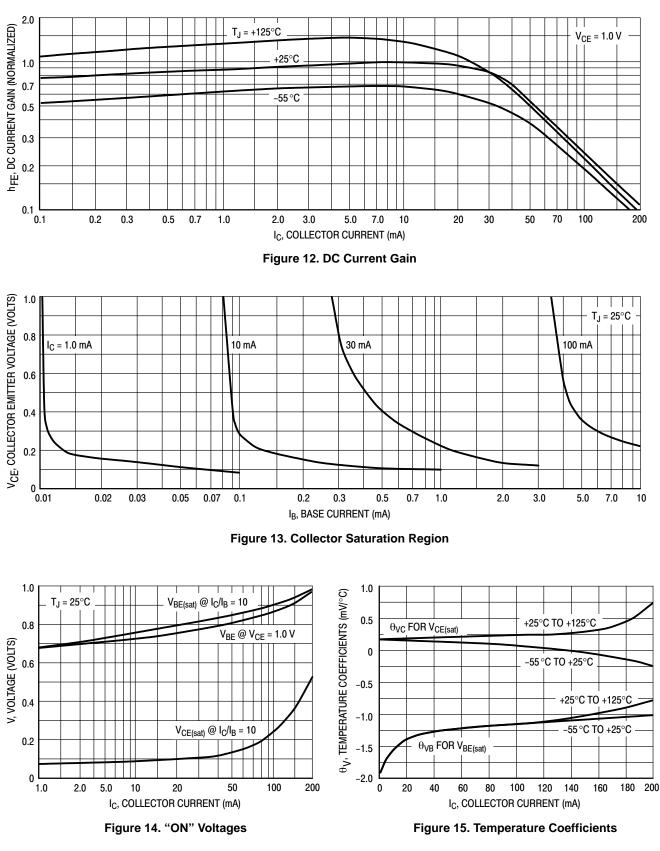

#### ON CHARACTERISTICS (Note 2)

| $ \begin{array}{l} \mbox{DC Current Gain} \\ (I_C = -0.1 \mbox{ mAdc}, V_{CE} = -1.0 \mbox{ Vdc}) \\ (I_C = -1.0 \mbox{ mAdc}, V_{CE} = -1.0 \mbox{ Vdc}) \\ (I_C = -10 \mbox{ mAdc}, V_{CE} = -1.0 \mbox{ Vdc}) \\ (I_C = -50 \mbox{ mAdc}, V_{CE} = -1.0 \mbox{ Vdc}) \\ (I_C = -100 \mbox{ mAdc}, V_{CE} = -1.0 \mbox{ Vdc}) \\ \end{array} $ | h <sub>FE</sub>      | 60<br>80<br>100<br>60<br>30 | -<br>-<br>300<br>- | -   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------------|--------------------|-----|

| Collector - Emitter Saturation Voltage<br>( $I_C = -10 \text{ mAdc}, I_B = -1.0 \text{ mAdc}$ )<br>( $I_C = -50 \text{ mAdc}, I_B = -5.0 \text{ mAdc}$ )                                                                                                                                                                                         | V <sub>CE(sat)</sub> | -                           | -0.25<br>-0.4      | Vdc |

| Base - Emitter Saturation Voltage<br>$(I_C = -10 \text{ mAdc}, I_B = -1.0 \text{ mAdc})$<br>$(I_C = -50 \text{ mAdc}, I_B = -5.0 \text{ mAdc})$                                                                                                                                                                                                  | V <sub>BE(sat)</sub> | -0.65<br>-                  | -0.85<br>-0.95     | Vdc |

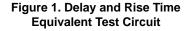

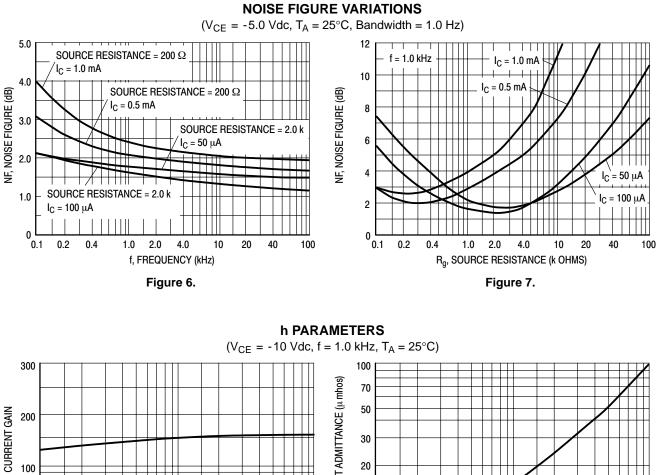

#### SMALL- SIGNAL CHARACTERISTICS

| Current - Gain - Bandwidth Product                                                                              | f <sub>T</sub>   | 250 | -    | MHz                 |

|-----------------------------------------------------------------------------------------------------------------|------------------|-----|------|---------------------|

| Output Capacitance                                                                                              | C <sub>obo</sub> | -   | 4.5  | pF                  |

| Input Capacitance                                                                                               | C <sub>ibo</sub> | -   | 10.0 | pF                  |

| Input Impedance<br>(V <sub>CE</sub> = -10 Vdc, I <sub>C</sub> = -1.0 mAdc, f = 1.0 kHz)                         | h <sub>ie</sub>  | 2.0 | 12   | kΩ                  |

| Voltage Feedback Ratio<br>(V <sub>CE</sub> = -10 Vdc, I <sub>C</sub> = -1.0 mAdc, f = 1.0 kHz)                  | h <sub>re</sub>  | 0.1 | 10   | X 10 <sup>- 4</sup> |

| Small- Signal Current Gain<br>(V <sub>CE</sub> = -10 Vdc, I <sub>C</sub> = -1.0 mAdc, f = 1.0 kHz)              | h <sub>fe</sub>  | 100 | 400  | -                   |

| Output Admittance<br>(V <sub>CE</sub> = -10 Vdc, I <sub>C</sub> = -1.0 mAdc, f = 1.0 kHz)                       | h <sub>oe</sub>  | 3.0 | 60   | μmhos               |

| Noise Figure<br>(V <sub>CE</sub> = -5.0 Vdc, I <sub>C</sub> = -100 μAdc, R <sub>S</sub> = 1.0 k Ω, f = 1.0 kHz) | NF               | -   | 4.0  | dB                  |

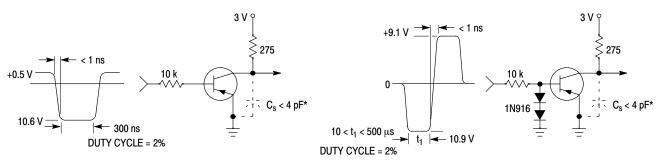

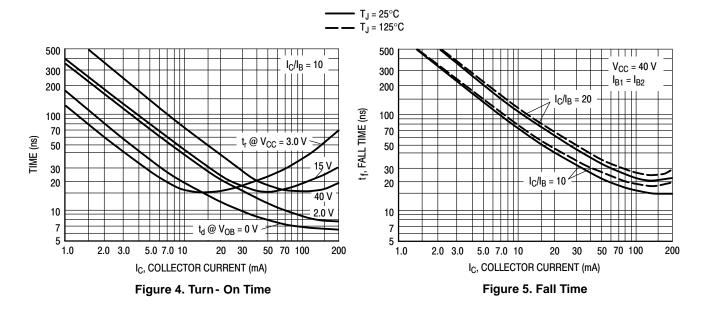

#### SWITCHING CHARACTERISTICS

| Delay Time   | (V <sub>CC</sub> = -3.0 Vdc, V <sub>BE</sub> = 0.5 Vdc)  | t <sub>d</sub> | - | 35  |    |

|--------------|----------------------------------------------------------|----------------|---|-----|----|

| Rise Time    | (I <sub>C</sub> = -10 mAdc, I <sub>B1</sub> = -1.0 mAdc) | t <sub>r</sub> | - | 35  | ns |

| Storage Time | $(V_{CC} = -3.0 \text{ Vdc}, I_C = -10 \text{ mAdc})$    | t <sub>s</sub> | - | 225 |    |

| Fall Time    | (I <sub>B1</sub> = I <sub>B2</sub> = -1.0 mAdc)          | t <sub>f</sub> | - | 75  | ns |

2. Pulse Test: Pulse Width  $\leq$  300 µs; Duty Cycle  $\leq$  2.0%.

\* Total shunt capacitance of test jig and connectors

Figure 2. Storage and Fall Time Equivalent Test Circuit

**TYPICAL AUDIO SMALL-SIGNAL CHARACTERISTICS**

### **TYPICAL STATIC CHARACTERISTICS**

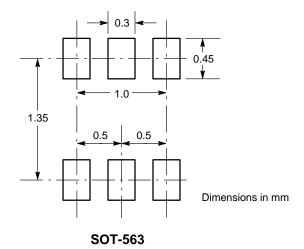

# INFORMATION FOR USING THE SOT-563 SURFACE MOUNT PACKAGE MINIMUM RECOMMENDED FOOTPRINT FOR SURFACE MOUNTED APPLICATIONS

Surface mount board layout is a critical portion of the total design. The footprint for the semiconductor packages must be the correct size to insure proper solder connection

interface between the board and the package. With the correct pad geometry, the packages will self align when subjected to a solder reflow process.

The power dissipation of the SOT-563 is a function of the pad size. This can vary from the minimum pad size for soldering to a pad size given for maximum power dissipation. Power dissipation for a surface mount device is determined by  $T_{J(max)}$ , the maximum rated junction temperature of the die,  $R_{\theta JA}$ , the thermal resistance from the device junction to ambient, and the operating temperature,  $T_A$ . Using the values provided on the data sheet for the SOT-563 package,  $P_D$  can be calculated as follows:

$$P_{D} = \frac{T_{J(max)} - T_{A}}{R_{\theta JA}}$$

The values for the equation are found in the maximum ratings table on the data sheet. Substituting these values into the equation for an ambient temperature  $T_A$  of 25°C, one can calculate the power dissipation of the device which in this case is 150 milliwatts.

$$P_{D} = \frac{150^{\circ}C - 25^{\circ}C}{833^{\circ}C/W} = 150 \text{ milliwatts}$$

The 833°C/W for the SOT-563 package assumes the use of the recommended footprint on a glass epoxy printed circuit board to achieve a power dissipation of 150 milliwatts. There are other alternatives to achieving higher power dissipation from the SOT-563 package. Another alternative would be to use a ceramic substrate or an aluminum core board such as Thermal Clad<sup>®</sup>. Using a board material such as Thermal Clad, an aluminum core board, the power dissipation can be doubled using the same footprint.

#### SOLDERING PRECAUTIONS

The melting temperature of solder is higher than the rated temperature of the device. When the entire device is heated to a high temperature, failure to complete soldering within a short time could result in device failure. Therefore, the following items should always be observed in order to minimize the thermal stress to which the devices are subjected.

- Always preheat the device.

- The delta temperature between the preheat and soldering should be 100°C or less.\*

- When preheating and soldering, the temperature of the leads and the case must not exceed the maximum temperature ratings as shown on the data sheet. When using infrared heating with the reflow soldering method, the difference shall be a maximum of 10°C.

- The soldering temperature and time shall not exceed 260°C for more than 10 seconds.

- When shifting from preheating to soldering, the maximum temperature gradient shall be 5°C or less.

- After soldering has been completed, the device should be allowed to cool naturally for at least three minutes. Gradual cooling should be used as the use of forced cooling will increase the temperature gradient and result in latent failure due to mechanical stress.

- Mechanical stress or shock should not be applied during cooling.

\* Soldering a device without preheating can cause excessive thermal shock and stress which can result in damage to the device

Thermal Clad is a registered trademark of the Bergquist Company.

NDTES:

# onsemí

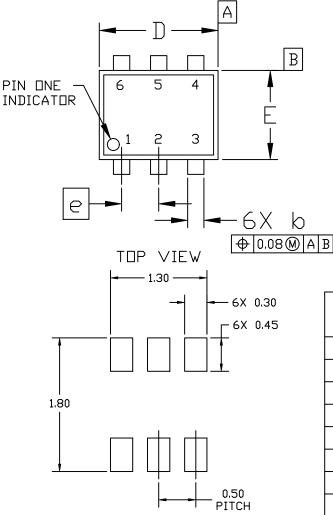

6Х

(

MILLIMETERS

NDM.

0.55

0.22

0.13

1.60

1.20

0.50 BSC

0.20

1.60

MAX.

0.60

0.27

0.18

1.70

1.30

0.30

1.70

SIDE VIEW

MIN.

0.50

0.17

0.08

1.50

1.10

0.10

1.50

SOT-563, 6 LEAD CASE 463A ISSUE H

DATE 26 JAN 2021

SCALE 4:1

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 2009.

- 2. CONTROLLING DIMENSION: MILLIMETERS

- 3. MAXIMUM LEAD THICKNESS INCLUDES LEAD FINISH THICKNESS. MINIMUM LEAD THICKNESS IS THE MINIMUM THICKNESS OF BASE MATERIAL.

А

DIM

Α

b

С

D

Ε

e L

Η<sub>E</sub>

RECOMMENDED MOUNTING FOOTPRINT\* For additional information on our Pb-Free strategy and soldering details, please download the DN Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

| DOCUMENT NUMBER: | 98AON11126D     | Electronic versions are uncontrolled except when accessed directly from<br>Printed versions are uncontrolled except when stamped "CONTROLLED ( |             |

|------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | SOT-563, 6 LEAD |                                                                                                                                                | PAGE 1 OF 2 |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights of others.

ж

# DUSEM

#### SOT-563, 6 LEAD CASE 463A ISSUE H

DATE 26 JAN 2021

| GENERIC          |  |  |  |  |

|------------------|--|--|--|--|

| MARKING DIAGRAM* |  |  |  |  |

|   |       | 1 |

|---|-------|---|

|   | XX M• |   |

| 4 | 0     |   |

| 1 |       |   |

XX = Specific Device Code

M = Month Code

= Pb-Free Package .

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "•", may or may not be present. Some products may not follow the Generic Marking.

| STYLE 1:                                                                                      | STYLE 2:                                                                                                    | STYLE 3:         |

|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------------------|

| PIN 1. EMITTER 1                                                                              | PIN 1. EMITTER 1                                                                                            | PIN 1. CATHIDE 1 |

| 2. BASE 1                                                                                     | 2. EMITTER 2                                                                                                | 2. CATHIDE 1     |

| 3. COLLECTOR 2                                                                                | 3. BASE 2                                                                                                   | 3. ANIDE/ANIDE 2 |

| 4. EMITTER 2                                                                                  | 4. COLLECTOR 2                                                                                              | 4. CATHIDE 2     |

| 5. BASE 2                                                                                     | 5. BASE 1                                                                                                   | 5. CATHIDE 2     |

| 6. COLLECTOR 1                                                                                | 6. COLLECTOR 1                                                                                              | 6. ANIDE/ANIDE 1 |

| STYLE 4:                                                                                      | STYLE 5:                                                                                                    | STYLE 6:         |

| PIN 1. COLLECTOR                                                                              | PIN 1. CATHODE                                                                                              | PIN 1. CATHIDE   |

| 2. COLLECTOR                                                                                  | 2. CATHODE                                                                                                  | 2. ANIDE         |

| 3. BASE                                                                                       | 3. ANODE                                                                                                    | 3. CATHIDE       |

| 4. EMITTER                                                                                    | 4. ANODE                                                                                                    | 4. CATHIDE       |

| 5. COLLECTOR                                                                                  | 5. CATHODE                                                                                                  | 5. CATHIDE       |

| 6. COLLECTOR                                                                                  | 6. CATHODE                                                                                                  | 6. CATHIDE       |

| STYLE 7:                                                                                      | STYLE 8:                                                                                                    | STYLE 9:         |

| PIN 1. CATHODE                                                                                | PIN 1. DRAIN                                                                                                | PIN 1. SDURCE 1  |

| 2. ANODE                                                                                      | 2. DRAIN                                                                                                    | 2. GATE 1        |

| 3. CATHODE                                                                                    | 3. GATE                                                                                                     | 3. DRAIN 2       |

| 4. CATHODE                                                                                    | 4. SEURCE                                                                                                   | 4. SDURCE 2      |

| 5. ANODE                                                                                      | 5. DRAIN                                                                                                    | 5. GATE 2        |

| 6. CATHODE                                                                                    | 6. DRAIN                                                                                                    | 6. DRAIN 1       |

| STYLE 10:<br>PIN 1. CATHIDE 1<br>2. N/C<br>3. CATHIDE 2<br>4. ANIDE 2<br>5. N/C<br>6. ANIDE 1 | STYLE 11:<br>PIN 1. EMITTER 2<br>2. BASE 2<br>3. COLLECTOR 1<br>4. EMITTER 1<br>5. BASE 1<br>6. COLLECTOR 2 |                  |

| DOCUMENT NUMBER: | 98AON11126D Electronic versions are uncontrolled except when accessed directly from the Document Repos<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |  |             |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------|

| DESCRIPTION:     | SOT-563, 6 LEAD                                                                                                                                                                           |  | PAGE 2 OF 2 |

|                  |                                                                                                                                                                                           |  |             |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent\_Marking.pdf</u>. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or indental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification. Buyer shall indemnify and hold onsemi and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs,

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

Technical Library: www.onsemi.com/design/resources/technical-documentation onsemi Website: www.onsemi.com

ONLINE SUPPORT: <u>www.onsemi.com/support</u> For additional information, please contact your local Sales Representative at <u>www.onsemi.com/support/sales</u>