**TPD4S214**

SLVSBR1F - JANUARY 2013-REVISED JANUARY 2015

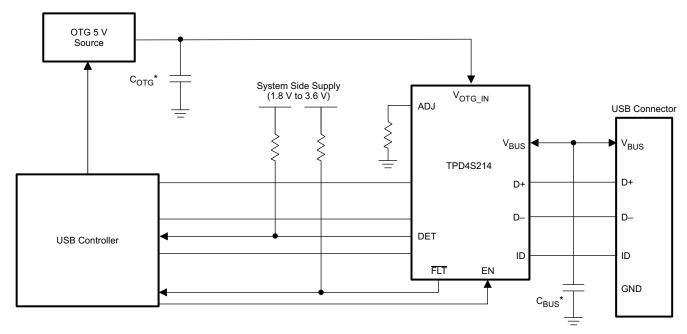

# TPD4S214 USB OTG Companion Device with V<sub>BUS</sub> Over Voltage Protection, Over Current Protection, and Four Channel ESD Protection

#### **Features**

- Input Voltage Protection at V<sub>BUS</sub> from -7 V to 30 V

- IEC61000-4-2 Level 4 ESD Protection

- ±15-kV Contact Discharge

- ±15-kV Air Gap Discharge

- IEC 61000-4-5 Surge Protection

- 7.8 A (8/20 µs)

- Low R<sub>DS(ON)</sub> N-CH FET Switch for High Efficiency

- Compliant with USB2.0 and USB3.0 OTG spec

- User Adjustable Current Limit From 250 mA to Beyond 1.2 A

- **Built-in Soft-start**

- Reverse Current Blocking

- Over Voltage Lock Out for V<sub>BUS</sub>

- Under Voltage Lock Out for Vota IN

- Thermal Shutdown and Short Circuit Protection

- Auto Retry on any Fault; No Latching Off States

- Integrated V<sub>BUS</sub> Detection Circuit

- Low Capacitance TVS ESD Clamp for USB2.0 High Speed Data Rate

- Internal 16ms Startup Delay

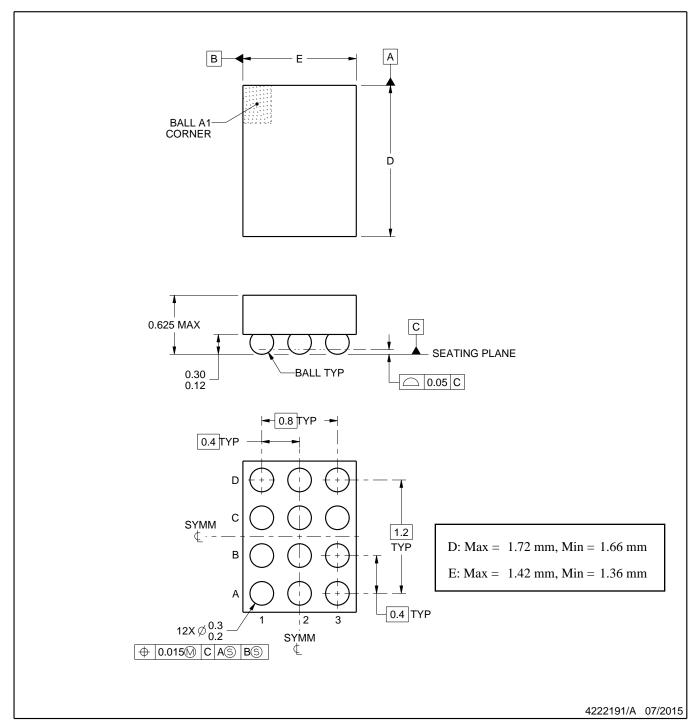

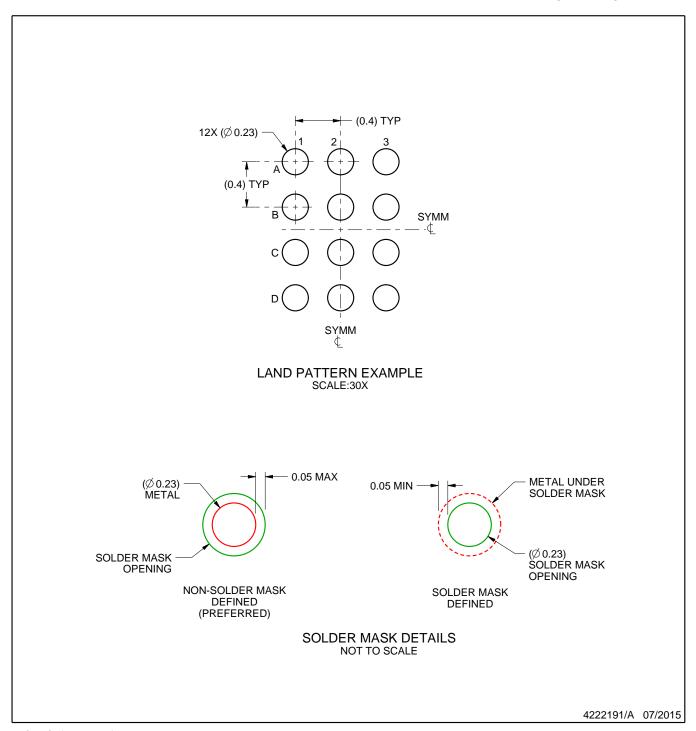

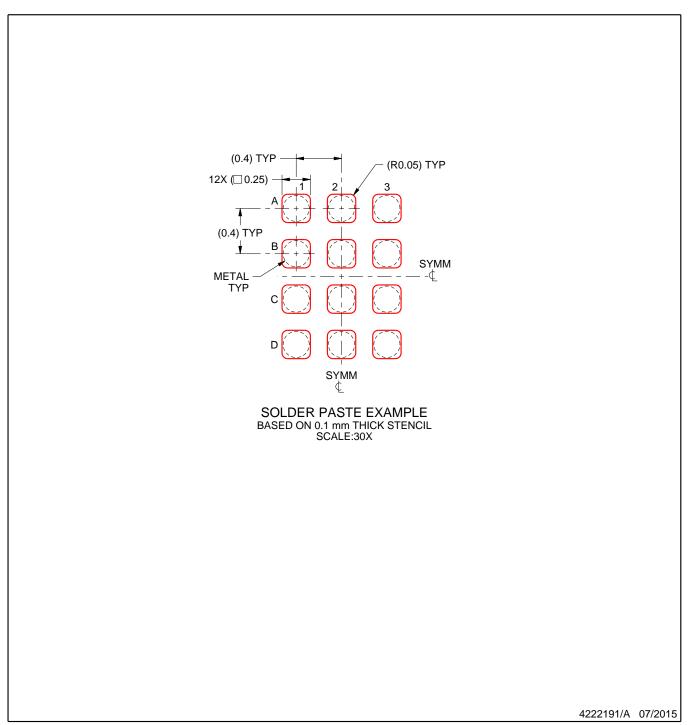

- Space Saving WCSP (12-YFF) Package

- UL Listed and CB File No. E169910

## **Applications**

- Cell Phones

- Tablet, eBook

- Portable Media Players

- Digital Camera

## 3 Description

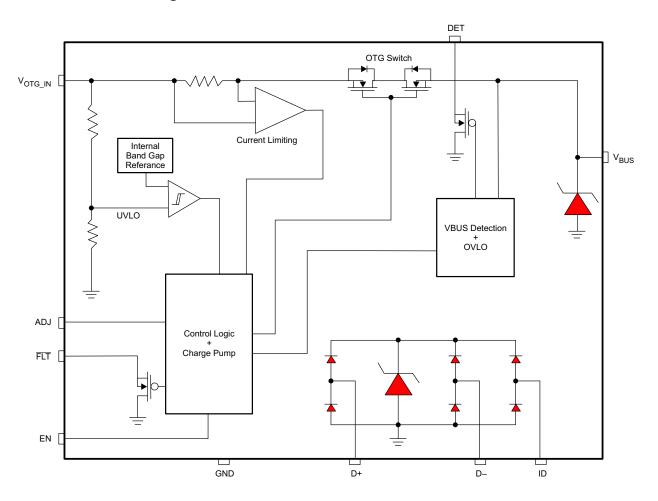

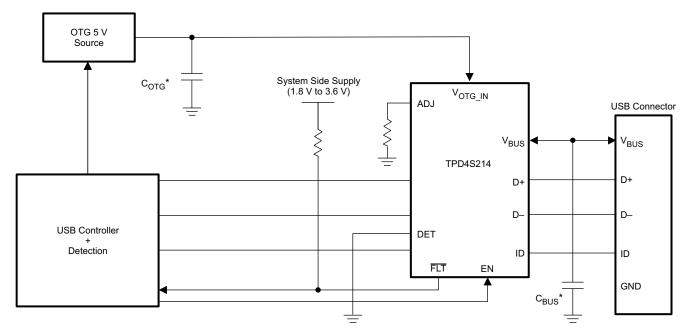

The TPD4S214 is a single-chip protection solution for USB On-the-Go (OTG) and other current limited USB applications. This device includes an integrated low R<sub>DS(ON)</sub> N-channel current limited switch for the OTG current supply to peripheral devices. TPD4S214 offers low capacitance transient voltage suppression (TVS) electrostatic discharge (ESD) clamping diodes for the D+, D-, and ID pins for both USB2.0 and USB3.0 applications. The  $V_{\text{BUS}}$  pin can handle continuous voltage ranging from -7~V to 30 V. The over voltage lock-out (OVLO) at the V<sub>BUS</sub> pin ensures that if there is a fault condition at the V<sub>BUS</sub> line, TPD4S214 is able to isolate it and protect the internal circuitry from damage. Similarly, the under voltage lock out (UVLO) at the V<sub>OTG\_IN</sub> pin ensures that there is no power drain from the internal OTG supply to external  $V_{BUS}$  if  $V_{OTG\_IN}$  droops below a safe operating level. When EN is high, the OTG switch is activated and the FLT pin indicates whether there is a fault condition. The soft start feature waits 16 ms to turn on the OTG switch after all operating conditions are met.

## Device Information<sup>(1)</sup>

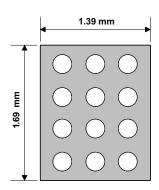

| PART NUMBER | PACKAGE   | BODY SIZE (MAX)   |  |  |

|-------------|-----------|-------------------|--|--|

| TPD4S214    | WCSP (12) | 1 39 mm x 1 69 mm |  |  |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

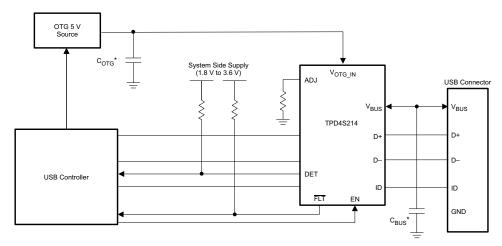

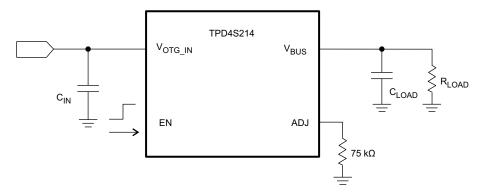

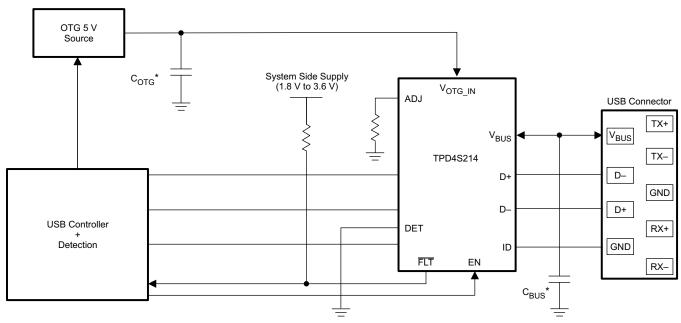

## Simplified Schematic

Features ...... 1

Applications ...... 1

7.12 Typical Characteristics ...... 8 8 Detailed Description ...... 11

## **Table of Contents**

| 4                          | Description 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8.1 Overview                                                                                         | 11               |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------------------|

| E                          | Simplified Schematic1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8.2 Functional Block Diagram                                                                         | 11               |

| 5                          | Revision History2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8.3 Feature Description                                                                              | 12               |

| 6                          | Pin Configuration and Functions3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8.4 Device Functional Modes                                                                          | 17               |

| 7                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9 Application and Implementation                                                                     | 18               |

| •                          | 7.1 Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 9.1 Application Information                                                                          | 18               |

|                            | 7.2 ESD Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9.2 Typical Application                                                                              | 18               |

|                            | 7.3 Recommended Operating Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 10 Power Supply Recommendations                                                                      | <mark>2</mark> 2 |

|                            | 7.4 Thermal Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 11 Layout                                                                                            | 22               |

|                            | 7.5 Thermal Shutdown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 11.1 Layout Guidelines                                                                               | 22               |

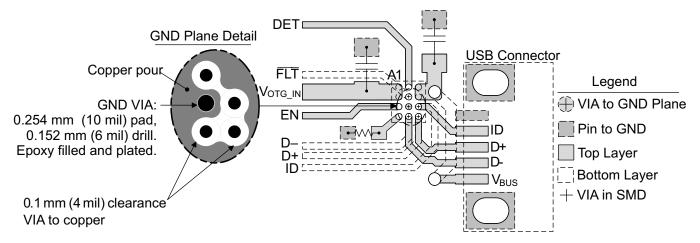

|                            | 7.6 Electrical Characteristics for EN, FLT, DET, D+, D-,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 11.2 Layout Example                                                                                  | 22               |

|                            | V <sub>BUS</sub> , ID Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 12 Device and Documentation Support                                                                  | 23               |

|                            | 7.7 Electrical characteristics for UVLO / OVLO 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 12.1 Documentation Support                                                                           |                  |

|                            | 7.8 Electrical Characteristics for DET Circuits 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 12.2 Trademarks                                                                                      |                  |

|                            | 7.9 Electrical Characteristics for OTG Switch 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 12.3 Electrostatic Discharge Caution                                                                 | 23               |

|                            | 7.10 Electrical Characteristics for Current Limit and Short                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 12.4 Glossary                                                                                        |                  |

|                            | Circuit Protection7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13 Mechanical, Packaging, and Orderable                                                              |                  |

|                            | 7.11 Supply Current Consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Information                                                                                          | 23               |

| P                          | Added UL and CB certifications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                      | 1                |

|                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                      |                  |

| ha                         | nges from Revision D (October 2014) to Revision E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                      | Page             |

| A                          | nges from Revision D (October 2014) to Revision E  Added R <sub>LOAD</sub> TEST CONDITIONS to I <sub>OCP</sub> in the Electrical Characteristics of the Electrical |                                                                                                      |                  |

| F                          | Added $R_{LOAD}$ TEST CONDITIONS to $I_{OCP}$ in the Electrical Ch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                      |                  |

| ha:                        | Added R <sub>LOAD</sub> TEST CONDITIONS to I <sub>OCP</sub> in the Electrical Ch<br>Protection table.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | unctional Modes, Application and Implementation ction, Device and Documentation Support section, and | 7<br>Page        |

| /<br>F<br>S<br>H<br>S<br>N | Added R <sub>LOAD</sub> TEST CONDITIONS to I <sub>OCP</sub> in the Electrical Chrotection table.  Inges from Revision C (August 2013) to Revision D  Handling Rating table, Feature Description section, Device Feetion, Power Supply Recommendations section, Layout settlement of the Electrical Chromatical | unctional Modes, Application and Implementation ction, Device and Documentation Support section, and | Page             |

| H<br>S<br>N                | Added R <sub>LOAD</sub> TEST CONDITIONS to I <sub>OCP</sub> in the Electrical Chrotection table.  Inges from Revision C (August 2013) to Revision D  Handling Rating table, Feature Description section, Device Feetion, Power Supply Recommendations section, Layout settlement of the Electrical Chromatical | unctional Modes, Application and Implementation ction, Device and Documentation Support section, and | Page             |

| Han                        | Added R <sub>LOAD</sub> TEST CONDITIONS to I <sub>OCP</sub> in the Electrical Chrotection table.  Inges from Revision C (August 2013) to Revision D  Handling Rating table, Feature Description section, Device Feetion, Power Supply Recommendations section, Layout set Mechanical, Packaging, and Orderable Information section.  Inges from Original (January 2013) to Revision A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | unctional Modes, Application and Implementation ction, Device and Documentation Support section, and | Page             |

| Heshar                     | Added R <sub>LOAD</sub> TEST CONDITIONS to I <sub>OCP</sub> in the Electrical Chorotection table.  Inges from Revision C (August 2013) to Revision D  Handling Rating table, Feature Description section, Device Feetion, Power Supply Recommendations section, Layout selection, Packaging, and Orderable Information section.  Inges from Original (January 2013) to Revision A  Changed the Product Preview data sheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | unctional Modes, Application and Implementation ction, Device and Documentation Support section, and | Page Page        |

| Has<br>has<br>has<br>chas  | Added R <sub>LOAD</sub> TEST CONDITIONS to I <sub>OCP</sub> in the Electrical Chorotection table.  Inges from Revision C (August 2013) to Revision D  Handling Rating table, Feature Description section, Device Feetion, Power Supply Recommendations section, Layout selection, Packaging, and Orderable Information section.  Inges from Original (January 2013) to Revision A  Changed the Product Preview data sheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | unctional Modes, Application and Implementation ction, Device and Documentation Support section, and | Page Page        |

Product Folder Links: TPD4S214

Submit Documentation Feedback

# 6 Pin Configuration and Functions

TPD4S214 WCSP (YFF) PIN MAPPING TOP SIDE/SEE-THROUGH VIEW)

| TOP SIDE/SEE-THROUGH VIEW |                     |     |                  |  |  |

|---------------------------|---------------------|-----|------------------|--|--|

|                           | 1                   | 2   | 3                |  |  |

| А                         | V <sub>OTG_N</sub>  | DET | V <sub>BUS</sub> |  |  |

| В                         | V <sub>OTG_IN</sub> | FLT | V <sub>BUS</sub> |  |  |

| С                         | EN                  | GND | ID               |  |  |

| D                         | ADJ                 | D-  | D+               |  |  |

## **Pin Functions**

| NAME                | PIN    | TYPE   | DESCRIPTION                                                                                      |  |  |  |  |  |

|---------------------|--------|--------|--------------------------------------------------------------------------------------------------|--|--|--|--|--|

| D-                  | D2     | I/O    | USB data-                                                                                        |  |  |  |  |  |

| D+                  | D3     | I/O    | USB data+                                                                                        |  |  |  |  |  |

| ID                  | C3     | I/O    | USB ID signal                                                                                    |  |  |  |  |  |

| FLT                 | B2     | 0      | Open-Drain Output. Connect a pull-up resistor from FLT to the supply voltage of the host system. |  |  |  |  |  |

| ADJ                 | D1     | I      | Attach external resistor to adjust the current limit                                             |  |  |  |  |  |

| EN                  | C1     | I      | Enable Input. Drive EN high to enable the OTG switch.                                            |  |  |  |  |  |

| V <sub>BUS</sub>    | A3, B3 | 0      | USB Power Output                                                                                 |  |  |  |  |  |

| V <sub>OTG_IN</sub> | A1, B1 | I      | USB OTG Supply Input                                                                             |  |  |  |  |  |

| DET                 | A2     | 0      | Open-Drain Output. Connect a pull-up resistor from DET to the supply voltage of the host system. |  |  |  |  |  |

| GND                 | C2     | Ground | Connect to PCB ground plane                                                                      |  |  |  |  |  |

## 7 Specifications

## 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                   |                                                                | MIN  | MAX | UNIT |

|-----------------------------------|----------------------------------------------------------------|------|-----|------|

| T <sub>stg</sub>                  | Storage temperature range                                      | -40  | 85  | °C   |

| V <sub>OTG_IN</sub> , ADJ, EN     | Input voltage                                                  | -0.5 | 7   | V    |

| V <sub>BUS</sub>                  | Output voltage to USB connector                                | -7   | 30  | V    |

| FLT, DET                          | Output voltage                                                 | -0.5 | 7   | V    |

|                                   | Input clamp current V <sub>I</sub> < 0                         |      | -50 | mA   |

|                                   | I <sub>OUT</sub> Continuous current through FLT and DET output |      | 10  | mA   |

|                                   | I <sub>GND</sub> Continuous current through GND                |      | 100 | mA   |

|                                   | T <sub>J(max)</sub> maximum junction temperature               | -65  | 150 | °C   |

| D+, D-, ID, V <sub>BUS</sub> pins | IEC 61000-4-2 Contact Discharge at 25°C                        |      | ±15 | kV   |

| D+, D-, ID, V <sub>BUS</sub> pins | IEC 61000-4-2 Air-gap Discharge at 25°C                        |      | ±15 | kV   |

| D+, D-, ID pins                   | Peak Pulse Current (tp = 8/20 µs) at 25°C                      |      | 7.8 | Α    |

| D+, D-, ID pins                   | Peak Pulse Power (tp = 8/20 μs) at 25°C                        |      | 84  | W    |

<sup>(1)</sup> Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions*. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 7.2 ESD Ratings

|        |                                                                  |                                                                               |                                   | VALUE                                 | UNIT |  |

|--------|------------------------------------------------------------------|-------------------------------------------------------------------------------|-----------------------------------|---------------------------------------|------|--|

|        | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins (1) |                                                                               | ±2000                             | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |      |  |

| \/     | V <sub>(ESD)</sub> Electrostatic discharge                       | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins (2) |                                   | ±500                                  | V    |  |

| V(ESD) |                                                                  | IEC 61000-4-2 Contact Discharge                                               | D. D. ID. V. Dina                 | .15000                                | \/   |  |

|        |                                                                  | IEC 61000-4-2 Air-gap Discharge                                               | D+, D-, ID, V <sub>BUS</sub> Pins | ±15000                                | V    |  |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Pins listed as 2000 V may actually have higher performance.

## 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                         |                                                         |                                                                 | MIN  | TYP | MAX | UNIT |

|-------------------------|---------------------------------------------------------|-----------------------------------------------------------------|------|-----|-----|------|

| T <sub>A</sub>          | Operating free-air temperature                          |                                                                 | -40  |     | 85  | °C   |

| V <sub>IH</sub>         | High-level input voltage EN                             | High-level input voltage EN                                     |      |     |     | V    |

| V <sub>IL</sub>         | Low-level input voltage EN                              |                                                                 |      |     | 0.4 | V    |

| t <sub>EN</sub>         | EN ramp rate for proper turn on                         | Valid ramp rate is between 10 µs and 100 ms, rising and falling | 0.01 |     | 100 | ms   |

| t <sub>UVLO_SLEW</sub>  | V <sub>OTG_IN</sub> ramp rate for proper UVLO operation | Valid ramp rate is between 10 µs and 100 ms, rising and falling | 0.01 |     | 100 | ms   |

| t <sub>OVLO_SLEW</sub>  | V <sub>BUS</sub> ramp rate for proper OVLO operation    | Valid ramp rate is between 10 µs and 100 ms, rising and falling | 0.01 |     | 100 | ms   |

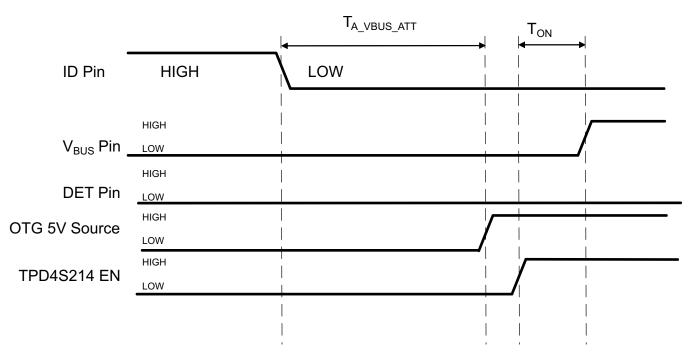

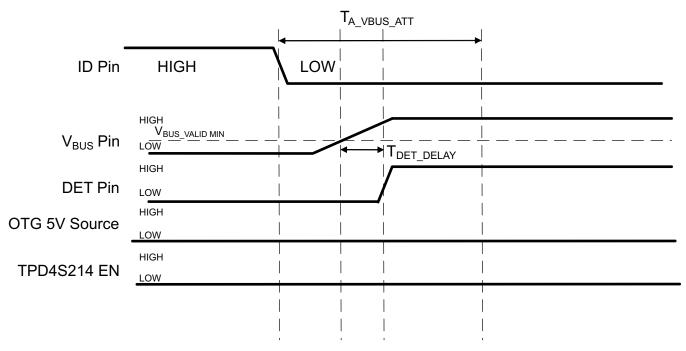

| T <sub>A_VBUS_ATT</sub> | Time to detect V <sub>BUS</sub> device attachme         | ent and turn on DET                                             |      |     | 200 | ms   |

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Pins listed as 500 V may actually have higher performance.

## 7.4 Thermal Information

|                        | THERMAL METRIC <sup>(1)</sup>                | YFF     | UNIT |

|------------------------|----------------------------------------------|---------|------|

|                        |                                              | 12 PINS |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 89.1    |      |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 0.5     |      |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 40.0    | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter   | 3.0     |      |

| ΨЈВ                    | Junction-to-board characterization parameter | 39.0    |      |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

## 7.5 Thermal Shutdown

over operating free-air temperature range (unless otherwise noted)

|                     | PARAMETER                              | TEST CONDITIONS                                                                                  | TYP | MAX  | UNIT |

|---------------------|----------------------------------------|--------------------------------------------------------------------------------------------------|-----|------|------|

| T <sub>SHDN+</sub>  | Shutdown temp rising                   |                                                                                                  | 141 |      | °C   |

| T <sub>SHDN</sub> - | Shutdown temp falling                  |                                                                                                  | 125 |      | ٥С   |

| T <sub>HYST</sub>   | Thermal-shutdown Hysteresis            |                                                                                                  | 16  |      | ٥С   |

| P <sub>MAX</sub>    | Maximum power dissipation              | $V_{OTG\_IN} = 5 \text{ V}, R_{load} = 5 \Omega, EN = 5 \text{ V}, R_{ADJ} = 75 \text{ K}\Omega$ |     | 0.16 | W    |

| $T_{JMAX}$          | Junction Temp at max power dissipation |                                                                                                  |     | 150  | °C   |

# 7.6 Electrical Characteristics for EN, FLT, DET, D+, D-, V<sub>BUS</sub>, ID Pins

over operating free-air temperature range (unless otherwise noted)

|                     | PARAMETER                                                | TEST CONDITIONS                                                                                  | MIN | TYP | MAX  | UNIT |

|---------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----|-----|------|------|

| I <sub>IL_EN</sub>  | EN pin input leakage current                             | EN = 3.3 V                                                                                       |     |     | 1    | μΑ   |

| I <sub>OL</sub>     | FLT, DET pin output leakage current                      | FLT, DET = 3.6 V                                                                                 |     |     | 1    | μΑ   |

| V <sub>OL_FLT</sub> | Low-level output voltage FLT                             | $V_{BUS}$ or $V_{OTG\_IN}$ = 5 V or 0 V $I_{OL}$ = 100 $\mu A$                                   |     |     | 100  | mV   |

| V <sub>OL_DET</sub> | Low-level output voltage DET                             | $V_{BUS}$ and $V_{OTG\_IN}$ = 5 V or 0 V $I_{OL}$ = 100 $\mu A$                                  |     |     | 100  | mV   |

| C <sub>EN</sub>     | Enable capacitance                                       | V <sub>BIAS</sub> = 1.8 V, f = 1 MHz, 30 mVpp ripple, V <sub>OTG_IN</sub> = 5 V                  |     | 4.5 |      | pF   |

| V <sub>D</sub>      | Diode forward voltage D+, D-, ID pins; lower clamp diode | I <sub>O</sub> = 8 mA                                                                            |     |     | 0.95 | V    |

| $I_{L_D}$           | Leakage current on D+, D-, ID Pins                       | D+, D-, ID = 3.3 V                                                                               |     |     | 100  | nA   |

| ΔC <sub>IO</sub>    | Differential capacitance between the D+, D-lines         | $V_{BIAS} = 1.8 \text{ V}, f = 1 \text{ MHz}, 30 \text{ mVpp ripple}, V_{OTG\_IN} = 5 \text{ V}$ |     |     | 0.04 | pF   |

| 0                   | Capacitance to GND for the D+, D- lines                  | // 4.0.\/ 6.4.MH= 20.00\/00 ========= // 5.1                                                     |     | 1.9 |      |      |

| C <sub>IO</sub>     | Capacitance to GND for the ID lines                      | $V_{BIAS} = 1.8 \text{ V}, f = 1 \text{ MHz}, 30 \text{ mVpp ripple}, V_{OTG\_IN} = 5 \text{ V}$ |     | 1.9 |      | pF   |

| V                   | Breakdown voltage D+, D-, ID pins                        | I <sub>br</sub> = 1 mA                                                                           | 6   |     |      | V    |

| $V_{BR}$            | Breakdown voltage on V <sub>BUS</sub>                    | I <sub>br</sub> = 1 mA                                                                           | 33  |     |      | V    |

| R <sub>DYN</sub>    | Dynamic on resistance D+, D-, ID clamps                  |                                                                                                  |     | 1   |      | Ω    |

## 7.7 Electrical characteristics for UVLO / OVLO

over operating free-air temperature range (unless otherwise noted)

|                        | PARAMETER                                                      | TEST CONDITIONS                                                                                                                                                         | MIN  | TYP  | MAX  | UNIT |

|------------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| INPUT UNDER            | R-VOLTAGE LOCKOUT                                              |                                                                                                                                                                         |      |      |      |      |