#### **Features**

- Precision low voltage monitoring

- 200 ms (typical) reset timeout

- · Watchdog timer with 1.6 sec timeout

- Manual reset input

- Reset output stage

- · Push-pull active-low

- Low power consumption: 2.2 μA

- Guaranteed reset output valid to V<sub>CC</sub> = 1 V

- · Power supply glitch immunity

- Specified from -40°C to +125°C

- 5-lead SOT-23 package

### **Applications**

- Microprocessor systems

- Computers

- Controllers

- · Intelligent instruments

- · Portable equipment

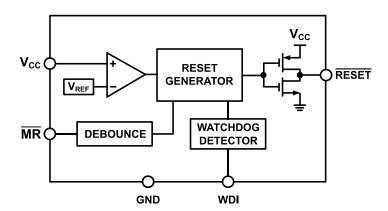

### **Description**

The TPV6823 is a supervisory circuit that monitors power supply voltage levels and provides a power-on reset signal.

It also has on-chip watchdog timer, which can give out a reset signal if the microprocessor fails to strobe watchdog timer within a preset timeout period.

A reset signal can also be asserted by an external manual reset input.

The reset and watchdog timeout periods are fixed at 200 ms (typical) and 1.6 sec (typical), respectively.

The TPV6823 is available in a 5-lead SOT-23 package and typically consumes only 2.2  $\mu$ A, suitable for use in low power, portable applications.

### **Typical Application Circuit**

### **Table of Contents**

| Features                                |    |

|-----------------------------------------|----|

| Applications                            | 1  |

| Description                             | 1  |

| Typical Application Circuit             | 1  |

| Revision History                        | 3  |

| Pin Configuration and Functions         | 4  |

| Pin Functions                           | 4  |

| Specifications                          | է  |

| Absolute Maximum Ratings                | 5  |

| ESD, Electrostatic Discharge Protection | 5  |

| Electrical Characteristics              | 6  |

| Electrical Characteristics              | 7  |

| Typical Performance Characteristics     |    |

| Detailed Description                    | 10 |

| Theory of Operation                     | 10 |

| Application Note                        | 11 |

| Tape and Reel Information               | 12 |

| Package Outline Dimensions              | 13 |

| SOT23-5                                 | 13 |

| Order Information                       | 14 |

### **Revision History**

| Date       | Revision | Notes                                  |  |  |  |

|------------|----------|----------------------------------------|--|--|--|

| 2018-12-10 | Rev.A.0  | First Release Version                  |  |  |  |

| 2019-04-15 | Rev.A.1  | Update package POD information         |  |  |  |

| 2019-05-28 | Rev.A.2  | Add WDI pulse interval spec            |  |  |  |

| 2021-08-26 | Rev.A.3  | Update Format and add Application Note |  |  |  |

| 2021-11-22 | Rev.A.4  | Correct POD                            |  |  |  |

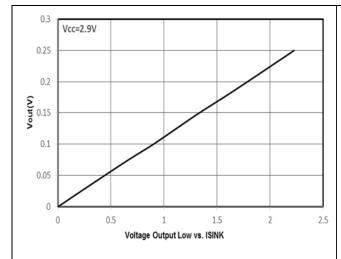

### **Pin Configuration and Functions**

#### **Pin Functions**

| Pin |       | 1/0 | Description                                                                                                                                                                                                         |  |  |

|-----|-------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| No. | Name  | I/O | Description                                                                                                                                                                                                         |  |  |

| 1   | RESET | 0   | Active-Low Reset Push-Pull Output Stage. Asserted whenever $V_{\text{CC}}$ is below the reset threshold, $V_{\text{TH}}$ .                                                                                          |  |  |

| 2   | GND   | ı   | Ground.                                                                                                                                                                                                             |  |  |

| 3   | MR    | I   | Manual Reset Input. This is an active-low input, which, when forced low for at least 1 $\mu$ s, generates a reset. It features a 50 $k\Omega$ internal pull-up.                                                     |  |  |

| 4   | WDI   | I   | Watchdog Input. Generates a reset if the voltage on the pin remains low or high for the duration of the watchdog timeout. The timer is cleared if a logic transition occurs on this pin or if a reset is generated. |  |  |

| 5   | VCC   | -   | Power Supply Voltage Being Monitored.                                                                                                                                                                               |  |  |

### **Specifications**

#### **Absolute Maximum Ratings**

|                  | Parameter                           | Min  | Max | Unit |

|------------------|-------------------------------------|------|-----|------|

| Input Voltage    | VCC                                 | -0.3 | 6   | V    |

| Output Current   | RESET                               |      | 20  | mA   |

| TJ               | Maximum Junction Temperature        | -40  | 125 | °C   |

| T <sub>STG</sub> | Storage Temperature Range           | -65  | 150 | °C   |

| TL               | Lead Temperature (Soldering 10 sec) |      | 260 | °C   |

**Note:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

- (1) This data was taken with the JEDEC low effective thermal conductivity test board.

- (2) This data was taken with the JEDEC standard multilayer test boards.

#### **ESD, Electrostatic Discharge Protection**

|   | Symbol | Parameter                | Condition                             | Minimum Level | Unit |

|---|--------|--------------------------|---------------------------------------|---------------|------|

|   | HBM    | Human Body Model ESD     | ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | 4000          | V    |

| ſ | CDM    | Charged Device Model ESD | ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | 2000          | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### **Electrical Characteristics**

All test condition is  $V_{CC}$  = 1.53 V to 5.5 V,  $T_A$  = -40°C to +125°C, unless otherwise noted.

| Symbol                         | Parai                                   | meter           | Conditions                                          | Min          | Тур                            | Max                      | Unit       |

|--------------------------------|-----------------------------------------|-----------------|-----------------------------------------------------|--------------|--------------------------------|--------------------------|------------|

| Supply Vo                      | Itage and Curren                        | t               |                                                     |              |                                |                          |            |

| Vcc                            | VCC Operating Vo                        | oltage Range    |                                                     | 1            |                                | 5.5                      | V          |

| I <sub>CC</sub> Supply Current |                                         |                 | WDI and MR unconnected (VCC=1.8V)                   |              | 2.2                            | 10                       | μA         |

|                                | 1                                       |                 | WDI and MR unconnected (VCC=5V)                     |              | 6                              | 15                       | μA         |

|                                |                                         | TPV6823V        |                                                     | 1.51         | 1.58                           | 1.63                     | V          |

|                                |                                         | TPV6823W        |                                                     | 1.62         | 1.67                           | 1.71                     | V          |

|                                |                                         | TPV6823Y        |                                                     | 2.12         | 2.19                           | 2.25                     | V          |

|                                |                                         | TPV6823Z        |                                                     | 2.25         | 2.32                           | 2.38                     | V          |

| $V_{TH}$                       | Reset Threshold<br>Voltage              | TPV6823R        |                                                     | 2.55         | 2.63                           | 2.70                     | V          |

|                                | voltage                                 | TPV6823S        |                                                     | 2.85         | 2.93                           | 3.00                     | V          |

|                                |                                         | TPV6823T        |                                                     | 3.00         | 3.08                           | 3.15                     | V          |

|                                |                                         | TPV6823M        |                                                     | 4.25         | 4.38                           | 4.5                      | V          |

|                                |                                         | TPV6823L        |                                                     | 4.5          | 4.63                           | 4.75                     | V          |

|                                | Reset Threshold Temperature Coefficient |                 |                                                     |              | 60                             |                          | ppm/<br>°C |

| V <sub>HYS</sub>               | Reset Threshold Hysteresis              |                 |                                                     |              | $2 \times \frac{V_{TH}}{1000}$ |                          | mV         |

| t <sub>RD</sub>                | VCC To Reset De                         | lay             | V <sub>TH</sub> - V <sub>CC</sub> = 100mV           |              | 20                             |                          | μs         |

| t <sub>RP</sub>                | Reset Timeout Pe                        | riod            |                                                     | 140          | 200                            | 280                      | ms         |

| Vol                            | Reset Output Volta<br>Pull)             | age Low (Push-  | V <sub>CC</sub> ≥ 1V, I <sub>SINK</sub> = 50µA      |              |                                | 0.3                      | V          |

| Vон                            | Reset Output Volta<br>Pull Only)        | age High (Push- | V <sub>CC</sub> ≥ 1.8V, I <sub>SOURCE</sub> = 200µA | 0.8 ×<br>Vcc |                                |                          | V          |

| MR Pin                         |                                         |                 |                                                     |              |                                |                          | •          |

| VIL_MR                         | Input Threshold Voltage Low for MR      |                 |                                                     |              |                                | 0.3 ×<br>V <sub>CC</sub> | ٧          |

| V <sub>IH_MR</sub>             | Input Threshold Voltage High for MR     |                 |                                                     | 0.7 ×<br>Vcc |                                |                          | ٧          |

| t <sub>PW_MR</sub>             | MR Input Pulse Width                    |                 |                                                     | 1            |                                |                          | μs         |

| t <sub>GR_MR</sub>             | MR Glitch Rejection                     |                 |                                                     |              | 100                            |                          | ns         |

| t <sub>d_MR</sub>              | MR to Reset Dela                        | y               |                                                     |              | 200                            |                          | ns         |

| R <sub>PU_MR</sub>             | MR Pull-Up Resis                        | tance           |                                                     |              | 50                             |                          | kΩ         |

\*Note: 100% tested at  $T_A = 25$ °C.

#### **Electrical Characteristics**

All test condition is  $V_{CC}$  = 1.53 V to 5.5 V,  $T_A$  = -40°C to +125°C, unless otherwise noted.

| Symbol              | Parameter               | Conditions                         | Min                   | Тур | Max                      | Unit |

|---------------------|-------------------------|------------------------------------|-----------------------|-----|--------------------------|------|

| WDI Pin             |                         |                                    |                       |     |                          |      |

| t <sub>WD</sub>     | Watchdog Timeout Period |                                    | 1.12                  | 1.6 | 2.4                      | s    |

| t <sub>PW_WD</sub>  | WDI Pulse Width 50 ns   |                                    | 50                    |     |                          | ns   |

| t <sub>int_WD</sub> | WDI Pulse Interval      |                                    | 12                    |     |                          | ms   |

| VIL_WD              | WDI Input Threshold VIL |                                    |                       |     | 0.3 ×<br>V <sub>cc</sub> | V    |

| V <sub>IH_WD</sub>  | WDI Input Threshold VIH |                                    | 0.7 × V <sub>CC</sub> |     |                          | V    |

| I <sub>WDI</sub>    | WDI I are at Ourse of   | V <sub>WDI</sub> = V <sub>CC</sub> |                       | 20  |                          | μΑ   |

|                     | WDI Input Current       | V <sub>WDI</sub> = 0               |                       | -15 |                          | μA   |

\*Note: 100% tested at T<sub>A</sub> = 25°C.

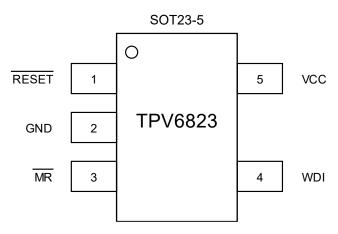

### **Typical Performance Characteristics**

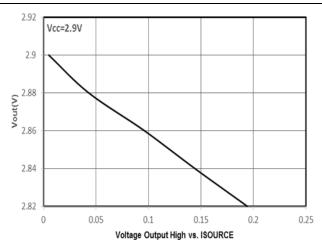

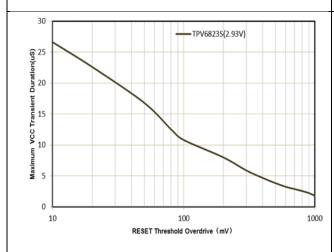

All test condition:  $V_{CC} = 3.3 \text{ V}$ ,  $T_A = +25^{\circ}\text{C}$ , RL =  $150\Omega$  to GND, unless otherwise noted.

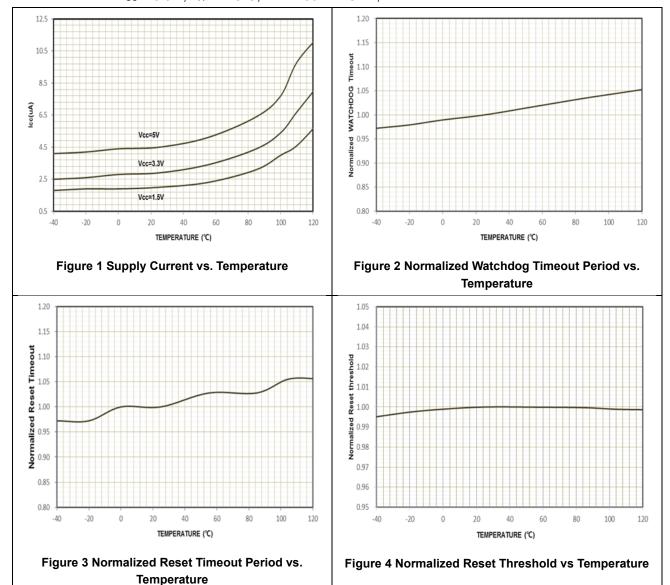

### **Typical Performance Characteristics (Continued)**

All test condition:  $V_{CC} = 3.3 \text{ V}$ ,  $T_A = +25^{\circ}\text{C}$ , RL = 150 $\Omega$  to GND, unless otherwise noted.

Figure 5 Voltage Output Low vs. ISINK

Figure 6 Voltage Output Low vs. ISOURCE

Figure 7 Maximum VCC Transient Duration vs. Reset Threshold Overdrive

Figure 8 Reset Output Voltage vs. Supply Voltage

#### **Detailed Description**

#### **Theory of Operation**

The TPV6823 provides supply voltage supervision as well as manual reset and watchdog functions.

A reset signal is asserted when the supply voltage is below a preset threshold. In addition, the TPV6823 allows supply voltage stabilization with a fixed timeout before the reset de-asserts after the supply voltage rises above the threshold.

A watchdog timer detects if the microprocessor code breaks down or becomes stuck in an infinite loop. If this happens, the watchdog timer asserts a reset pulse, which restarts the microprocessor in a known state.

A manual reset input is available to reset the microprocessor, for example, by using an external push-button.

#### **RESET OUTPUT**

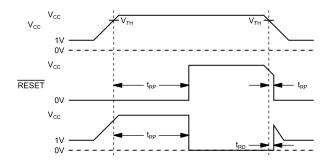

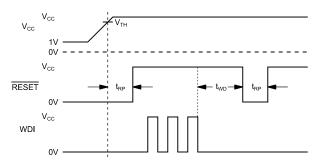

The TPV6823 features an active-low push-pull output. For active-low output, the reset signal is guaranteed to be logic low for  $V_{CC}$  down to 1 V. The reset output is asserted when  $V_{CC}$  is below the reset threshold ( $V_{TH}$ ), when  $\overline{MR}$  is driven low, or when WDI is not serviced within the watchdog timeout period ( $t_{WD}$ ). Reset remains asserted for the duration of the reset active timeout period ( $t_{RP}$ ) after  $V_{CC}$  rises above the reset threshold, after  $\overline{MR}$  transitions from low to high, or after the watchdog timer times out. Figure 9 shows the reset outputs.

Figure 9 Reset Timing Diagram

#### MANUAL RESET INPUT

The TPV6823 features a manual reset input ( $\overline{\text{MR}}$ ), which, when driven low, asserts the reset output. When  $\overline{\text{MR}}$  transitions from low to high, reset remains asserted for the duration of the reset active timeout period before deasserting.

The  $\overline{MR}$  input has an internal pull-up resistor so that the input is always high when unconnected. Noise immunity is provided on the  $\overline{MR}$  input, and fast, negative-going transients are ignored. A 0.1  $\mu F$  capacitor between  $\overline{MR}$  and ground provides additional noise immunity.

#### WATCHDOG INPUT

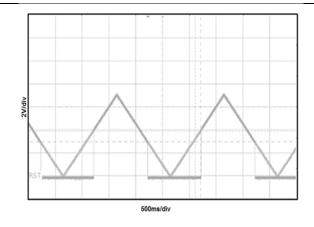

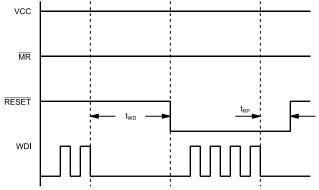

The TPV6823 features a watchdog timer, which monitors microprocessor activity. A timer circuit is cleared with every low-to-high or high-to-low logic transition on the watchdog input pin (WDI). If the timer counts through the preset watchdog timeout period ( $t_{WD}$ ), reset is asserted. The microprocessor is required to toggle the WDI pin to avoid being reset.

In addition to logic transitions on WDI, the watchdog timer is also cleared by a reset assertion due to an undervoltage condition on  $V_{CC}$  or  $\overline{MR}$  being pulled low. When reset is asserted, the watchdog timer is cleared and does not begin counting again until reset de-asserts. The watchdog timer can be disabled by leaving WDI

floating or by three-stating the WDI driver.

Figure 10 Watchdog Timing Diagram

### **Application Note**

#### Power up/down Restriction:

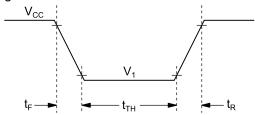

When power supply ramps up very slow at high temperature, there may be a certain percentage of the chips are probabilistic abnormal (With abnormal current appears around 0.6V, internal LDO is pulled down, and then the RESET output is incorrect). Through simulation and experiment, certain requirements of power supply up and down should be followed to avoid this kind of issue.

The requirements are shown in Figure 11:

Figure 11 Power Supply Requirements

- 1.  $V_1 < 200 \text{mV}$

- 2.  $t_{TH} > 40 \text{ms}$ ,

- 3.  $t_R > 0.2V/ms$

- 4. In power up duration ( $t_R$ ), Ripple or noise on  $V_{CC}$  should be < 100mV

#### **WDI Restriction:**

If WDI is kept to be low or high longer than  $\underline{t_{WD}}$  then the  $\overline{RESET}$  signal is triggered to be low. Only in this case, if WDI is toggled when  $\overline{RESET}$  is low, the  $\overline{RESET}$  will be kept low, until WDI is not toggled and kept to be low or high longer than  $t_{RP}$ , and then  $\overline{RESET}$  will recover to high again.

Figure 12 Watchdog Requirements

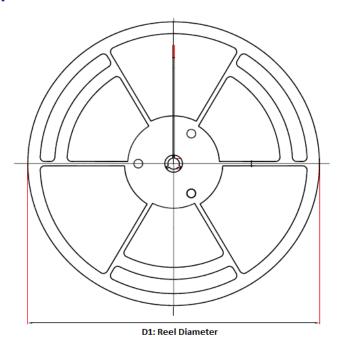

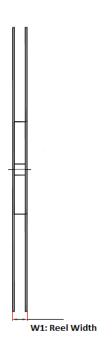

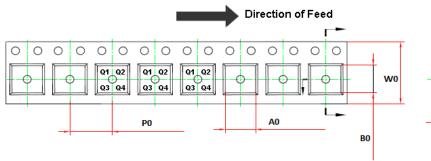

### **Tape and Reel Information**

| Order Number | Package | D1<br>(mm) | W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | W0<br>(mm) | Pin1<br>Quadrant |

|--------------|---------|------------|------------|------------|------------|------------|------------|------------|------------------|

| TPV6823V-TR  | SOT23-5 | 180        | 13.1       | 3.2        | 3.2        | 1.4        | 4          | 8          | Q3               |

| TPV6823W-TR  | SOT23-5 | 180        | 13.1       | 3.2        | 3.2        | 1.4        | 4          | 8          | Q3               |

| TPV6823Y-TR  | SOT23-5 | 180        | 13.1       | 3.2        | 3.2        | 1.4        | 4          | 8          | Q3               |

| TPV6823Z-TR  | SOT23-5 | 180        | 13.1       | 3.2        | 3.2        | 1.4        | 4          | 8          | Q3               |

| TPV6823R-TR  | SOT23-5 | 180        | 13.1       | 3.2        | 3.2        | 1.4        | 4          | 8          | Q3               |

| TPV6823S-TR  | SOT23-5 | 180        | 13.1       | 3.2        | 3.2        | 1.4        | 4          | 8          | Q3               |

| TPV6823T-TR  | SOT23-5 | 180        | 13.1       | 3.2        | 3.2        | 1.4        | 4          | 8          | Q3               |

| TPV6823M-TR  | SOT23-5 | 180        | 13.1       | 3.2        | 3.2        | 1.4        | 4          | 8          | Q3               |

| TPV6823L-TR  | SOT23-5 | 180        | 13.1       | 3.2        | 3.2        | 1.4        | 4          | 8          | Q3               |

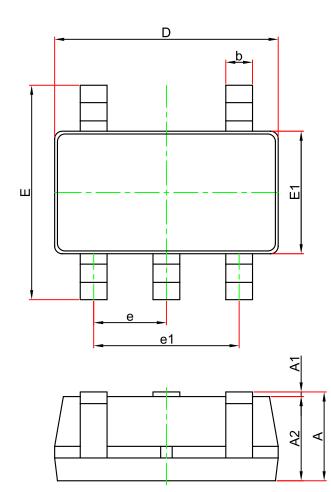

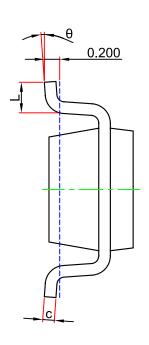

## Package Outline Dimensions

### **SOT23-5**

| Symbol | Dimensions | In Millimeters | Dimensions In Inches |       |  |

|--------|------------|----------------|----------------------|-------|--|

| Symbol | Min.       | Max.           | Min.                 | Max.  |  |

| Α      | 1.050      | 1.250          | 0.041                | 0.049 |  |

| A1     | 0.000      | 0.100          | 0.000                | 0.004 |  |

| A2     | 1.050      | 1.150          | 0.041                | 0.045 |  |

| b      | 0.300      | 0.500          | 0.012                | 0.020 |  |

| С      | 0.100      | 0.200          | 0.004                | 0.008 |  |

| D      | 2.820      | 3.020          | 0.111                | 0.119 |  |

| E1     | 1.500      | 1.700          | 0.059                | 0.067 |  |

| Е      | 2.650      | 2.950          | 0.104                | 0.116 |  |

| е      | 0.950      | 0.950 (BSC)    |                      | (BSC) |  |

| e1     | 1.800      | 2.000          | 0.071                | 0.079 |  |

| L      | 0.300      | 0.600          | 0.012                | 0.024 |  |

| θ      | 0°         | 8°             | 0°                   | 8°    |  |

### Low Voltage Supervisory

#### **Order Information**

| Order Number | Operating Temperature<br>Range | Package | Marking<br>Information | MSL | Transpor<br>Quar |

|--------------|--------------------------------|---------|------------------------|-----|------------------|

| TPV6823V-TR  | −40°C to 125°C                 | SOT23-5 | V1V                    | 1   | Tape and R       |

| TPV6823W-TR  | -40°C to 125°C                 | SOT23-5 | V1W                    | 1   | Tape and R       |

| TPV6823Y-TR  | −40°C to 125°C                 | SOT23-5 | V1Y                    | 1   | Tape and R       |

| TPV6823Z-TR  | −40°C to 125°C                 | SOT23-5 | V1Z                    | 1   | Tape and R       |

| TPV6823R-TR  | -40°C to 125°C                 | SOT23-5 | V1R                    | 1   | Tape and R       |

| TPV6823S-TR  | -40°C to 125°C                 | SOT23-5 | V1S                    | 1   | Tape and R       |

| TPV6823T-TR  | −40°C to 125°C                 | SOT23-5 | V1T                    | 1   | Tape and R       |

| TPV6823M-TR  | -40°C to 125°C                 | SOT23-5 | V1M                    | 1   | Tape and R       |

| TPV6823L-TR  | -40°C to 125°C                 | SOT23-5 | V1L                    | 1   | Tape and R       |

Green: 3PEAK defines "Green" to mean RoHS compatible and free of halogen substances.

<sup>3</sup>PEAK and the 3PEAK logo are registered trademarks of 3PEAK INCORPORATED. All of property of their respective owners.