# Micro/Mini USB Interface with Integrated 28V Charger

Check for Samples: LP8727

### **FEATURES**

- USB Multiplexing Switches

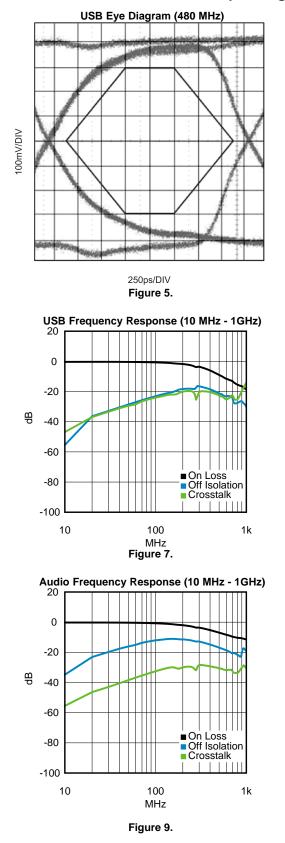

- High-Speed USB on USB and UART Inputs

- Negative Voltage Rail on Audio Inputs

- Internal LDO for ID Detection and MIC Bias

- Compatible with USB Charging **Specification Rev. 1.1**

- DSS Input for Default Switch Connection

- Low-Power MIC Standby Mode

- Linear Charge with Single Input

- 28 OVP on VBUS Input

- High-Current Mode for Production Test

- Thermal Regulation

- **Over-Voltage Protected LDO for USB** Transceivers and PMU Wakeup

- UVLO (Undervoltage Lock Out)

- Interrupt Request to Reduce SW Polling

- USB / ID Detection

- SEND / END Button Detection

- Mic Removal

- OVLO / UVLO on VBUS

- Charger Status

- **Thermal Shutdown Protection**

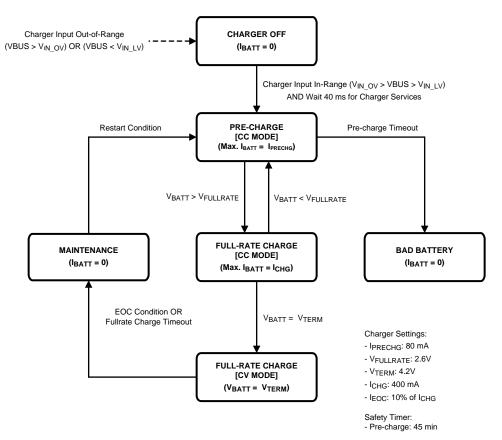

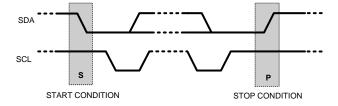

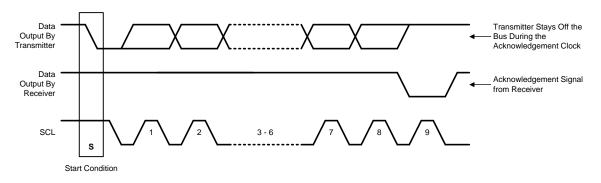

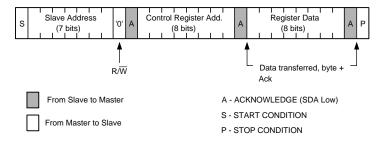

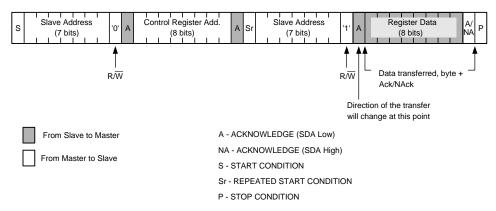

- I<sup>2</sup>C-compatible Serial Interface

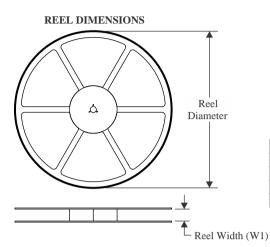

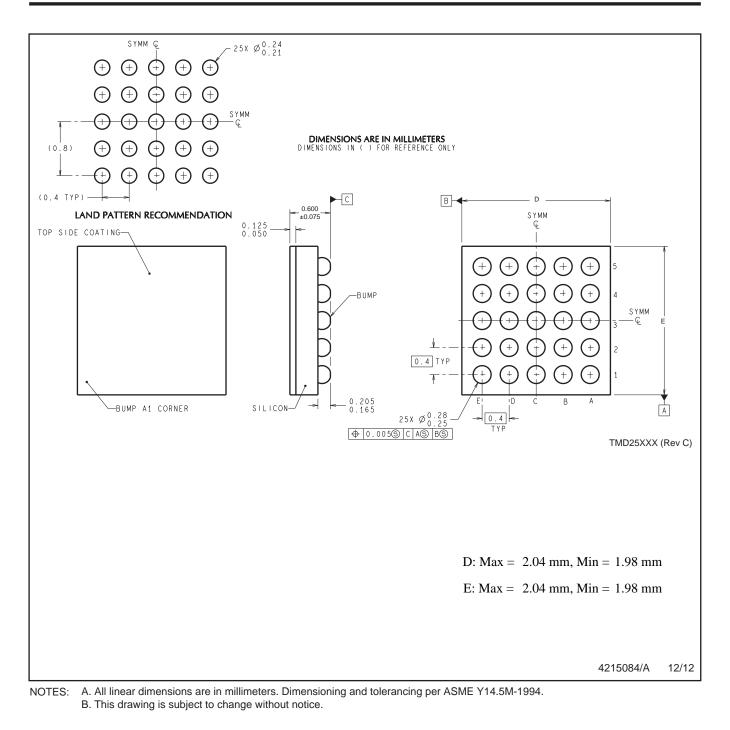

- 25-Bump 0.4 mm Pitch Thin DSBGA Package

### **APPLICATIONS**

- GSM, GPRS, EDGE, CDMA & WCDMA • handsets

- Portable Media Players / MP3 Players

### DESCRIPTION

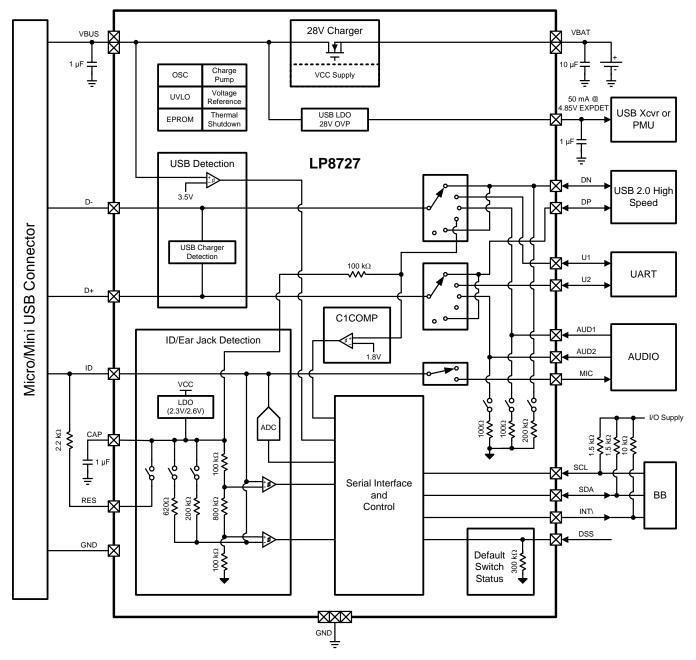

The LP8727 is designed to provide automatic multiplexing switches between Micro/Mini USB connector and USB, UART and Audio paths in cellular phone applications. It also contains a singleinput Li-Ion battery charger and an overvoltageprotected LDO. Programming is handled via an I<sup>2</sup>Ccompatible Serial Interface allowing control of charger, multiplexing switches, and reading status information of the device.

The multiplexing switches on USB and UART support high-speed USB, and Audio inputs can be driven to negative voltage rail. The LP8727 is compatible with USB charging specifications rev 1.1 from USB IF.

The Li-Ion charger requires few external components and integrates the power FET. Charging is thermally regulated to obtain the most efficient charging rate for a given ambient temperature. It has Overvoltage Protection (OVP) circuit at the charger input protects the PMU from input voltages up to +28V, eliminating the need for any external protection circuitry.

An overvoltage-protected LDO which can supply up to 50 mA is designed for powering up a low-voltage USB transceiver or waking up a PMU (Power Management Unit) when an external power source (either USB VBUS or wall adapter) is connected to the USB connector.

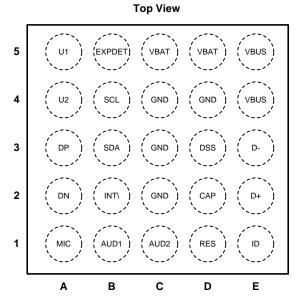

The LP8727 PMU is available in 25-bump 0.4 mm pitch thin DSBGA package (2.015 mm x 2.015 mm).

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

## **Typical Application Diagram**

### **Connection Diagram**

www.ti.com

Figure 1. 25-Bump (0.4mm Pitch) DSBGA Package

#### LP8727 PIN DESCRIPTIONS<sup>(1)</sup>

| PIN NAME | PIN #          | TYPE | DESCRIPTION                                                                                                                                    |  |  |  |

|----------|----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|          |                |      |                                                                                                                                                |  |  |  |

| AUD1     | B1             | AI   | Stereo Audio input (Left).                                                                                                                     |  |  |  |

| AUD2     | C1             | AI   | Stereo Audio input (Right).                                                                                                                    |  |  |  |

| CAP      | D2             | A    | Internal LDO output. Connect a 1.0 µF ceramic capacitor to GND.                                                                                |  |  |  |

| D-       | E3             | DI/O | Common data I/O. Connect to D- on Mini / Micro USB connector.                                                                                  |  |  |  |

| D+       | E2             | DI/O | Common data I/O. Connect to D+ on Mini / Micro USB connector.                                                                                  |  |  |  |

| DN       | A2             | DI/O | USB differential data I/O (-).                                                                                                                 |  |  |  |

| DP       | A3             | DI/O | USB differential data I/O (+).                                                                                                                 |  |  |  |

| DSS      | D3             | А    | Default switch status input. Internally pulled down with a 300 k $\Omega$ resistor. Logic high for UART startup and logic low for USB startup. |  |  |  |

| EXPDET   | B5             | Р    | Overvoltage protected LDO output for low-voltage USB system. Connect a 1.0 $\mu F$ ceramic capacitor to GND.                                   |  |  |  |

| GND      | C2, C3, C4, D4 | G    | Ground.                                                                                                                                        |  |  |  |

| ID       | E1             | DI   | USB ID Input. Connect to ID on Mini / Micro USB connector.                                                                                     |  |  |  |

| INT\     | B2             | DO   | Open-drain output for interrupt, active low. Typ. 10 k $\Omega$ pull-up resistor is required.                                                  |  |  |  |

| MIC      | A1             | AO   | Microphone output.                                                                                                                             |  |  |  |

| RES      | D1             | А    | Bias output for ID detection and Microphone. Connect a 2.2 k $\Omega$ resistor to ID pin.                                                      |  |  |  |

| SCL      | B4             | DI   | Serial interface clock input. Connect a 1.5 k $\Omega$ pullup resistor.                                                                        |  |  |  |

| SDA      | B3             | DI/O | Serial interface data input/output. Connect a 1.5 kΩ pullup resistor.                                                                          |  |  |  |

| U1       | A5             | DI/O | UART data Rx / USB differential data I/O (-).                                                                                                  |  |  |  |

| U2       | A4             | DI/O | UART data Tx / USB differential data I/O (+).                                                                                                  |  |  |  |

| VBAT     | C5, D5         | Р    | Main battery connection.<br>Requires 10 μF ceramic capacitor when a battery is not connected.                                                  |  |  |  |

| VBUS     | E4, E5         | Р    | USB VBUS input.                                                                                                                                |  |  |  |

(1) A: Analog Pin, D: Digital Pin, I: Input Pin, DI/O Digital Input/Output Pin, G: Ground, O: Output Pin, I/O: Input/Output Pin, P: Power Connection

#### SNVS898A-OCTOBER 2012-REVISED MAY 2013

www.ti.com

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### Absolute Maximum Ratings<sup>(1)(2)(3)(4)</sup>

|               | 0                      |                                                 |                                       |  |  |  |

|---------------|------------------------|-------------------------------------------------|---------------------------------------|--|--|--|

| INPUT VOLTAGE | VBUS to GND            | VBUS to GND                                     |                                       |  |  |  |

|               | VBAT, EXPDET, CAP [wrt | . GND]                                          | -0.3V to +6.0V                        |  |  |  |

|               | SCL, SDA, INT DSS [wrt | . GND]                                          | -0.3V to (V <sub>VBAT</sub> +0.3V)    |  |  |  |

|               | CP_EN = 1              | D+, D-, AUD1, AUD2                              | -2.1V to (V <sub>SWPOS)</sub> + 0.3V) |  |  |  |

|               |                        | DP, DN, U1, U2, ID, MIC, RES                    | -0.3V to (V <sub>SWPOS)</sub> + 0.3V) |  |  |  |

|               | $CP_EN = 0$            | D+, D-, DP, DN, AUD1, RES                       |                                       |  |  |  |

|               |                        | AUD2, U1, U2, ID, MIC                           | -0.3V to (V <sub>CC</sub> + 0.3V)     |  |  |  |

| TEMPERATURE   |                        | Junction Temperature (T <sub>J-MAX</sub> )      | 150°C                                 |  |  |  |

|               |                        | Storage Temperature Range                       | -65 to 150°C                          |  |  |  |

|               |                        | Maximum Lead<br>Temperature(Soldering, 10 sec.) | 260°C                                 |  |  |  |

(1) Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions under which operation of the device is ensured. Operating Ratings do not imply ensured performance limits. For ensured performance limits and associated test conditions, see the Electrical Characteristics tables.

All voltages are with respect to the potential at the GND pin.

(3) If Military/Aerospace specified devices are required, please contact the TI Sales Office/Distributors for availability and specifications.

Internal thermal shutdown circuitry protects the device fro permanent damage. Thermal shutdown engages at T<sub>J</sub> = 150°C (typ.) and (4) disengages at  $T_J = 130^{\circ}$ C. Also engages at 160°C and disengages 115°C.

### Operating Ratings<sup>(1)(2)</sup>

| INPUT VOLTAGE | VBAT                                                       | 2.5V to 5.5V   |

|---------------|------------------------------------------------------------|----------------|

|               | VBUS                                                       | 3.5V to 7V     |

| TEMPERATURE   | Junction Temperature (T <sub>J</sub> ) Range               | −40°C to 125°C |

|               | Ambient Temperature (T <sub>A</sub> ) Range <sup>(3)</sup> | −40°C to 85°C  |

(1) Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions under which operation of the device is ensured. Operating Ratings do not imply ensured performance limits. For ensured performance limits and associated test conditions, see the Electrical Characteristics tables.

(2) (3) All voltages are with respect to the potential at the GND pin.

In applications where high power dissipation and/or poor package resistance is present, the maximum ambient temperature may have to be de-rated. Maximum ambient temperature ( $T_A$ -MAX) is dependent on the maximum operating junction temperature ( $T_J$ -MAX), The maximum power dissipation of the device in the application (PD-MAX) and the junction to ambient thermal resistance of the package ( $\theta_{JA}$ ) in the application, as given by the following equation:  $T_A$ -MAX =  $T_J$ -MAX ( $\theta_{JA} \times PD$ -MAX). Due to the pulsed nature of testing the part, the temp in the Electrical Characteristic table is specified as  $T_A = T_J$ .

#### SNVS898A-OCTOBER 2012-REVISED MAY 2013

# ESD Rating<sup>(1)</sup>

www.ti.com

| VBUS, VBAT, D+ D-, ID | IEC61000-4-2 In-module  | ±8kV Contact Discharge |

|-----------------------|-------------------------|------------------------|

|                       | Testing @ USB Connector | ±15kV Air Discharge    |

| Human Body            |                         | ±2 kV                  |

| Machine Model         |                         | ±150V                  |

The human-body model is 100 pF discharged through 1.5 kΩ. The machine model is a 200 pF capacitor discharged directly into each pin, MIL-STD-883 3015.7.

#### **Thermal Properties**

| Junction-to-Ambient Thermal Resistance $(\theta_{JA})^{(1)}$<br>Thin DSBGA-25 | 46°C |

|-------------------------------------------------------------------------------|------|

|-------------------------------------------------------------------------------|------|

(1) Junction-to-ambient thermal resistance is highly application and board layout dependent. In applications where high power dissipation exists, special care must be given to thermal dissipation issues in board design.

# Electrical Characteristics<sup>(1)(2)</sup>

Limits in standard typeface are for  $T_J = 25^{\circ}$ C. Limits in **boldface** type apply over the operating ambient temperature range (-40°C  $\leq T_J \leq +125^{\circ}$ C). Unless otherwise noted, specifications apply to the Typical Application Circuit with  $V_{VBAT} = 3.7$ V,  $V_{VBUS} = 5$ V.

| Symbol               | Parameter Conditions            |                                                                              | Тур               | Min  | Max  | Units |  |

|----------------------|---------------------------------|------------------------------------------------------------------------------|-------------------|------|------|-------|--|

| / <sub>VBAT</sub>    | VBAT Voltage Range              |                                                                              |                   | 2.5  | 5.5  |       |  |

| / <sub>VBUS</sub>    | VBUS Voltage Range              |                                                                              |                   | 3.5  | 7    | V     |  |

| ,                    | latenal Ormata Maltana          | V <sub>VBUS</sub> = 5V                                                       | 4.2               |      |      |       |  |

| V <sub>CC</sub>      | Internal Supply Voltage         | $V_{VBUS} = 0V$                                                              | V <sub>VBAT</sub> |      |      |       |  |

| V <sub>SWPOS</sub>   | Positive Switch Regulator       | $V_{VBAT}$ > 3.6 or $V_{VBUS}$ > 3.6                                         | 3.4               | 3.3  | 3.6  | v     |  |

| V <sub>SWNEG</sub>   | Negative Switch Regulator       | $V_{VBAT}$ > 3.6 or $V_{VBUS}$ > 3.6                                         | -1.8              | -2.0 | -1.7 | v     |  |

| JNDERVOLTAC          | GE LOCKOUT                      |                                                                              |                   |      |      |       |  |

|                      | Undervoltage Lockout            | VBUS Rising (Default)                                                        | 3.9               | 3.7  | 4.1  |       |  |

| JVLO <sub>VBUS</sub> | Threshold range                 | VBUS Falling (Default)                                                       | 3.7               | 3.5  | 3.9  | V     |  |

| 11/1 0               | Undervoltage Lockout            | VBAT Rising (Default)                                                        | 2.9               | 2.7  | 3.1  | V     |  |

| UVLO <sub>VBAT</sub> | Threshold range                 | VBAT Falling (Default)                                                       | 2.7               | 2.5  | 2.9  | 1     |  |

| QUIESCENT CL         | JRRENTS                         |                                                                              |                   |      |      | 1     |  |

| VBAT (STBY)          | VBAT Standby I <sub>q</sub>     | CP_EN = ADC_EN = SEMREM = 0<br>USB_DET_DIS = 1                               | 3.8               |      | 20   |       |  |

| VBAT (SUP1)          | VBAT Supply Current1            | Register Default @ $V_{VBAT} = 3.7V$<br>$V_{VBUS} = 0V$                      | 42                |      | 90   | _     |  |

| VBAT (SUP2)          | VBAT Supply Current2            | Register Default @ $V_{VBAT}$ = 3.7V<br>ADC_EN = SEMREM = 1, $V_{VBUS}$ = 0V | 60                |      | 120  | μA    |  |

| VBUS (STBY)          | VBUS Standby I <sub>q</sub>     | CP_EN = ADC_EN = SEMREM = 0<br>USB_DET_DIS = CHG_OFF = 1,<br>EXPDET_EN = 0   | 90                |      | 200  |       |  |

| VBUS (SUP)           | VBUS Supply Current             | Register Default @V <sub>VBUS</sub> = 5V, No<br>load on VBAT (No battery)    | 250               |      | 400  |       |  |

| LOGIC AND CO         | NTROL INPUTS                    |                                                                              |                   |      |      |       |  |

| 1                    |                                 | SDA, SCL                                                                     |                   |      | 0.4  | V     |  |

| V <sub>IL</sub>      | Input Low Level                 | DSS                                                                          |                   |      | 0.4  | V     |  |

| 1                    | Input Lligh Lough               | SDA, SCL                                                                     |                   | 1.4  |      | v     |  |

| V <sub>IH</sub>      | Input High Level                | DSS                                                                          |                   | 1.4  |      | V     |  |

| LEAK                 | Input Current                   | All logic inputs<br>Over pin Voltage range                                   | -5                |      | +5   | μΑ    |  |

| DSSIN                | Input Resistance <sup>(2)</sup> | DSS Pulldown Resistor to GND                                                 | 300               |      |      | kΩ    |  |

(1) All voltages are with respect to the potential at the GND pin.

(2) Min and Max limits are specified by design, test or statistical analysis. Typical numbers are not ensured, but do represent the most likely norm.

# Electrical Characteristics<sup>(1)(2)</sup> (continued)

Limits in standard typeface are for  $T_J = 25^{\circ}$ C. Limits in **boldface** type apply over the operating ambient temperature range (-40°C ≤  $T_J ≤ +125^{\circ}$ C). Unless otherwise noted, specifications apply to the Typical Application Circuit with  $V_{VBAT} = 3.7$ V,  $V_{VBUS} = 5$ V.

| Symbol                | Parameter                                 | Conditions                                                                                                       | Тур | Min | Max | Units             |

|-----------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------------------|

| LOGIC AND CC          | ONTROL OUTPUTS                            |                                                                                                                  |     |     |     |                   |

| M                     |                                           | INT I <sub>OUT</sub> = 2mA                                                                                       |     |     | 0.4 | - V               |

| V <sub>OL</sub>       | Output Low Level                          | SDA, I <sub>SINK</sub> = 3mA                                                                                     |     |     | 0.4 | V                 |

| ID DETECTION          | LDO                                       |                                                                                                                  |     |     |     |                   |

| V <sub>OUT</sub>      | Output Voltage Accuracy                   | $I_{OUT} = 500 \ \mu\text{A}, \ V_{OUT} = 2.3 \text{V} \\ I_{OUT} = 500 \ \mu\text{A}, \ V_{OUT} = 2.6 \text{V}$ |     | -3  | +3  | %                 |

| I <sub>OUT</sub>      | Output Current Rating                     |                                                                                                                  |     |     | 1   | mA                |

| e <sub>N</sub>        | Output Noise Voltage                      | 10 Hz $\leq$ f $\leq$ 100 kHz<br>C <sub>OUT</sub> = 1µF <sup>(2)</sup>                                           | 15  |     |     | μV <sub>RMS</sub> |

| PSRR                  | Power Supply Ripple                       | $f = 10 \text{ kHz}, C_{OUT} = 1 \mu F$                                                                          | 75  |     |     | dB                |

| 1 OKK                 | Rejection Ratio                           | $I_{OUT} = 20 \text{ mA}^{(2)}$                                                                                  | 15  |     |     | 0.0               |

| C <sub>OUT</sub>      | External Output Capacitance for Stability | See <sup>(2)</sup>                                                                                               | 1.0 | 0.6 | 20  | μF                |

| EXPDET LDO            |                                           |                                                                                                                  |     |     |     |                   |

| V <sub>OUT</sub>      | Output Voltage Accuracy                   | $I_{OUT}$ = 1mA, $V_{OUT}$ = 4.85V @ $V_{VBUS}$ = 5V                                                             |     | -5  | +3  | %                 |

| V <sub>DO</sub>       | Dropout Voltage                           | I <sub>OUT</sub> = 50 mA @ V <sub>VBUS</sub> = 5V                                                                | 330 |     |     | mV                |

| I <sub>OUT(MAX)</sub> | Output Current Rating                     |                                                                                                                  |     |     | 50  | mA                |

| I <sub>SC</sub>       | Short Circuit Current Limit               | V <sub>OUT</sub> = 0V                                                                                            | 330 |     |     | mA                |

| C <sub>OUT</sub>      | External Output Capacitance for Stability | See <sup>(3)</sup>                                                                                               | 1.0 | 0.6 | 20  | μF                |

(3) Min and Max limits are specified by design, test or statistical analysis. Typical numbers are not ensured, but do represent the most likely norm.

## **Multiplexer Switches Electrical Characteristics**

Typical values and limits appearing in normal type apply for  $T_J=25$ °C. Unless otherwise noted,  $V_{VBAT} = 3.7V$ , VBUS is disconnected. Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $T_J = -40$ °C to +125°C.<sup>(1)</sup>

| Symbol                | Parameter                               | Conditions                                                   | Тур | Min  | Max                | Units |

|-----------------------|-----------------------------------------|--------------------------------------------------------------|-----|------|--------------------|-------|

|                       |                                         | CP_EN = 0                                                    |     | 0    | V <sub>CC</sub>    |       |

| V <sub>DP,DN</sub>    | Analog Signal Range                     | CP_EN = 1                                                    |     | 0    | V <sub>SWPOS</sub> | V     |

| R <sub>SWONUSB</sub>  | On Resistance                           |                                                              | 2.5 |      | 6                  |       |

| ΔR <sub>SWONUSB</sub> | On Resistance Match<br>Between Channels | $0V < V_{D+} \text{ or } V_{D-} < 1V$                        |     |      | 0.5                | Ω     |

| R <sub>FLATUSB</sub>  | On Resistance Flatness                  |                                                              | 0.5 |      |                    |       |

| ILEAKUSB(OFF)         | Off Leakage Current <sup>(2)</sup>      |                                                              |     | -360 | 360                | nA    |

| ILEAKUSB(ON)          | On Leakage Current <sup>(2)</sup>       | $$ 0V < V <sub>D+</sub> or V <sub>D-</sub> < 3.3V, CP_EN = 1 |     | -360 | -360 360           |       |

| UART ANALOG           | SWITCHES (U1, U2)                       |                                                              |     |      | ·                  |       |

| M                     | Angles Circol Dense                     | CP_EN = 0                                                    |     | 0    | V <sub>CC</sub>    | M     |

| V <sub>U1, U2</sub>   | Analog Signal Range                     | CP_EN = 1                                                    |     | 0    | V <sub>SWPOS</sub> | V     |

| R <sub>SWONART</sub>  | On Resistance                           |                                                              | 2.5 |      | 6                  |       |

| ΔR <sub>SWONART</sub> | On Resistance Match<br>Between Channels | $0V < V_{D+} \text{ or } V_{D-} < 1V$                        |     |      | 0.5                | Ω     |

| R <sub>FLATURT</sub>  | On Resistance Flatness                  |                                                              | 0.5 |      |                    |       |

(1) Junction-to-ambient thermal resistance is highly application and board layout dependent. In applications where high power dissipation exists, special care must be given to thermal dissipation issues in board design.

<sup>(2)</sup> Min and Max limits are specified by design, test or statistical analysis. Typical numbers are not ensured, but do represent the most likely norm.

SNVS898A-OCTOBER 2012-REVISED MAY 2013

#### www.ti.com

### **Multiplexer Switches Electrical Characteristics (continued)**

Typical values and limits appearing in normal type apply for  $T_J=25^{\circ}C$ . Unless otherwise noted,  $V_{VBAT} = 3.7V$ , VBUS is disconnected. Limits appearing in **boldface** type apply over the entire junction temperature range for operation,  $T_J = -40^{\circ}C$  to +125°C.<sup>(1)</sup>

| Symbol                   | Parameter                                          | Conditions                                                                                         | Тур  | Min                | Max                | Units |

|--------------------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------|------|--------------------|--------------------|-------|

| ILEAKUART(OFF)           | Off Leakage Current <sup>(2)</sup>                 |                                                                                                    |      | -360               | 360                |       |

| ILEAKUART(ON)            | On Leakage Current <sup>(2)</sup>                  | $0V < V_{D+} \text{ or } V_{D-} < 3.3V, CP_EN = 1$                                                 |      | -360               | 360                | nA    |

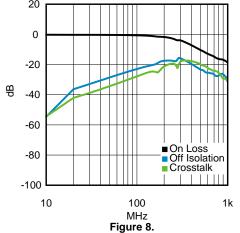

| AUDIO ANALOG             | SWITCHES (AUD1, AUD2)                              |                                                                                                    |      | *                  |                    |       |

|                          |                                                    | CP_EN = 0                                                                                          |      | 0                  | V <sub>CC</sub>    |       |

| V <sub>AUD1</sub> , AUD2 | Analog Signal Range                                | CP_EN = 1                                                                                          |      | V <sub>SWNEG</sub> | V <sub>SWPOS</sub> | V     |

| R <sub>SWONAUD</sub>     | On Resistance                                      |                                                                                                    | 1.6  |                    | 3.6                |       |

| ΔR <sub>SWONAUD</sub>    | On Resistance Match<br>Between Channels            | −1.8V < V <sub>D+</sub> or V <sub>D-</sub> < 1.8V                                                  |      |                    | 0.2                | Ω     |

| R <sub>FLATAUD</sub>     | On Resistance Flatness                             |                                                                                                    | 0.5  |                    |                    |       |

| ILEAKUAUD(OFF)           | Off Leakage Current <sup>(2)</sup>                 | $-1.8V < V_{D+}$ or $V_{D-} < 1.8V$ ,                                                              |      | -360               | 360                | - 4   |

| ILEAKUAUD(ON)            | On Leakage Current <sup>(2)</sup>                  | CP_EN = 1                                                                                          |      | -360               | 360                | nA    |

| R <sub>SHUNT</sub>       | Shunt Resistor                                     | I <sub>SHUNT</sub> = 10 mA                                                                         | 100  | 30                 | 180                | Ω     |

| MIC ANALOG S             | WITCHES (MIC)                                      |                                                                                                    |      |                    |                    |       |

|                          |                                                    | CP_EN = 0                                                                                          |      | 0                  | V <sub>CC</sub>    | V     |

| V <sub>MIC</sub>         | Analog Signal Range                                | CP_EN = 1                                                                                          |      | V <sub>SWNEG</sub> | V <sub>SWPOS</sub> |       |

| R <sub>SWONMIC</sub>     | On Resistance                                      |                                                                                                    | 3    |                    | 10                 | 0     |

| R <sub>FLATMIC</sub>     | On Resistance Flatness                             |                                                                                                    | 0.8  |                    |                    | Ω     |

| ILEAKMIC(OFF)            | Off Leakage Current <sup>(2)</sup>                 | 0V < V <sub>ID</sub> < 1.6V                                                                        |      | -360               | 360                | - 1   |

| ILEAKMIC(ON)             | On Leakage Current <sup>(2)</sup>                  |                                                                                                    |      | -360               | 360                | nA    |

| DYNAMIC                  |                                                    |                                                                                                    |      |                    |                    |       |

| T <sub>CP_EN</sub>       | Charge Pump Startup Time                           |                                                                                                    |      |                    | 1                  | ms    |

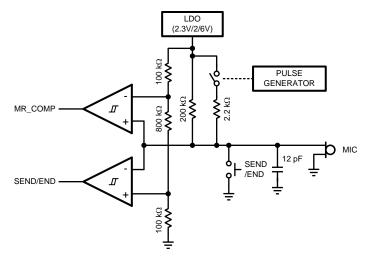

| T <sub>MICLPDP</sub>     | MIC Low-Power Detection<br>Pulse Time              |                                                                                                    | 117  | 50                 | 175                | μs    |

| T <sub>MICLPD</sub>      | MIC Low-Power Detection<br>Period                  | MIC_LP = 1, SEMREM = 1                                                                             | 100  | 45                 | 155                |       |

| T <sub>DEB</sub>         | Comparator Debounce Time                           |                                                                                                    | 60   | 30                 | 100                | ms    |

| T <sub>ONSW</sub>        | Analog Switch Turn-on Time                         |                                                                                                    |      |                    | 1                  |       |

| T <sub>OFFSW</sub>       | Analog Switch Turn-off Time                        | $RL = 50\Omega^{(3)(4)}$                                                                           |      |                    | 10                 |       |

| Т <sub>ВВМ</sub>         | Break-Before-Make                                  |                                                                                                    |      | 0                  |                    | μs    |

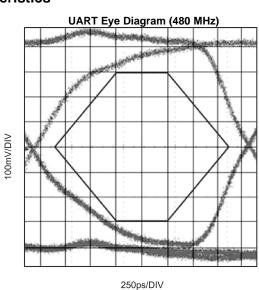

| V <sub>ISO</sub>         | Off-Isolation <sup>(5)</sup>                       | $R_{L} = 50\Omega, C_{L} = 5pF, f = 20 \text{ kHz}$                                                | -108 |                    |                    |       |

| V <sub>CT</sub>          | Crosstalk                                          | $V_{D+}$ or $V_{D-}=1V_{RMS}$ <sup>(6)(4)</sup>                                                    | -107 |                    |                    | dB    |

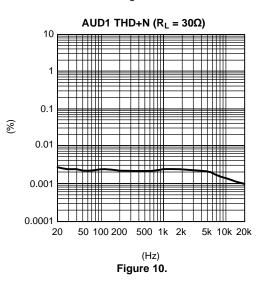

| THD+N <sub>AUD</sub>     | Total Harmonic Distortion<br>Plus Noise AUD1, AUD2 | $f$ = 20 Hz to 20 kHz, V V_{D+} or V_{D-}= 0.25V_{RMS}, R_L = 300, DC Bias = 0V, T = 25°C          | 0.05 |                    |                    | 9/    |

| AUD NI AUD               | Total Harmonic Distortion<br>Plus Noise MIC        | $f$ = 20 Hz to 20 kHz, V V_{D+} or V_{D=} 0.4V_{RMS}, R_L = 1k $\Omega$ , DC Bias = 0.8V, T = 25°C | 0.05 | 0.05               |                    | - %   |

(3) All timing is measured using 10% and 90% levels.

(4) Min and Max limits are specified by design, test or statistical analysis. Typical numbers are not ensured, but do represent the most likely norm.

Off-isolation = 20log [ $V_{D+/D-}$  / ( $V_{NO1/2}$  or  $V_{NC1/2}$ ),  $V_{D+/D-}$  = output,  $V_{NO1/2}$  or  $V_{NC1/2}$  = input to off switch. Crosstalk is measured between any two switches. (5)

(6)

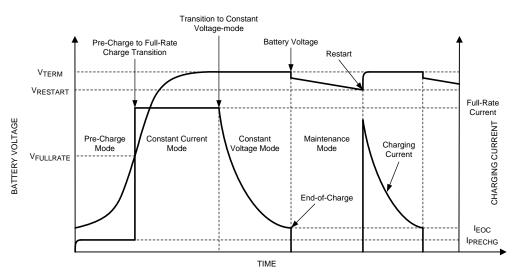

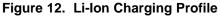

# **Charger Electrical Characteristics**

Typical values and limits in standard typeface are for  $T_J = 25^{\circ}C$ . Limits in **boldface** type apply over the entire junction temperature range (-40°C to +125°C).<sup>(1)(2)(3)</sup>

| Symbol                 | Parameter                                                    | Conditions                                                                                                                                                                                        | Тур | Min   | Max   | Units   |

|------------------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-------|---------|

| V <sub>OV</sub>        | Over Voltage Protection<br>Threshold                         | Charger input is turned off if voltage is above this threshold                                                                                                                                    | 6.9 | 6.7   | 7.2   | V       |

| V <sub>OV_HYS</sub>    | Over Voltage Protection<br>Threshold Hysteresis              |                                                                                                                                                                                                   | 170 | 120   | 220   | mV      |

| V <sub>VBUS</sub>      | VBUS Operating Range                                         |                                                                                                                                                                                                   |     | 4.45  | 6     | V       |

| V                      | VBUS OK Trip Point                                           | V <sub>VBUS</sub> - V <sub>VBAT</sub> (Rising)                                                                                                                                                    | 250 |       |       | mV      |

| V <sub>OK_CHG</sub>    | VB03 OK Hip Politi                                           | V <sub>VBUS</sub> - V <sub>VBAT</sub> (Falling)                                                                                                                                                   | 40  |       |       | IIIV    |

|                        | <b>T</b> 1 1 1 1 1                                           | $V_{\text{TERM}} = 4.2 \text{V}, \text{ I}_{\text{CHG}} = 50 \text{ mA}$                                                                                                                          |     | -0.35 | +0.35 |         |

| V <sub>TERM</sub>      | Termination Voltage                                          | V <sub>TERM</sub> is measured at 10% of the<br>programmed I <sub>CHG</sub> current                                                                                                                |     | -1    | +1    | %       |

| R <sub>DSON_CHG</sub>  | Charger pass transistor ON resistance                        | I <sub>CHG</sub> = 400 mA                                                                                                                                                                         | 250 |       | 400   | mΩ      |

| I <sub>CHG</sub>       | VBUS Programmable Full-<br>Rate Charging Current             | 4.45V $\leq$ V <sub>VBUS</sub> $\leq$ 6V<br>V <sub>VBAT</sub> $<$ V <sub>VBUS</sub> $-$ V <sub>OK_VBUS</sub><br>V <sub>FULL_RATE</sub> $<$ V <sub>VBAT</sub> $<$ V <sub>TERM</sub> <sup>(4)</sup> |     | 90    | 1100  | mA      |

|                        | Full-rate charging current tolerance                         | I <sub>CHG</sub> = 400 mA                                                                                                                                                                         |     | -5    | +5    | %       |

| I <sub>PRECHG</sub>    | Pre-charge current                                           | 2.2V < V <sub>VBAT</sub> < V <sub>FULL_RATE</sub><br>80 mA option selected                                                                                                                        | 80  | 60    | 100   | mA      |

| I <sub>VBUS(MAX)</sub> | Maximum Input Current                                        | $V_{VBUS}$ - $V_{VBAT} \le 0.8V$                                                                                                                                                                  |     |       | 2.3   | А       |

| V <sub>FULL_RATE</sub> | Full-rate Qualification<br>Threshold                         | V <sub>VBAT</sub> Rising, Transition from Pre-<br>charge to Full-rate Charging                                                                                                                    | 2.6 | 2.5   | 2.7   | V       |

| I <sub>EOC</sub>       | End-of-charge Current, % of Full-rate Current                | 0.1C option selected                                                                                                                                                                              | 10  |       |       | %       |

| T <sub>REG</sub>       | Regulated Junction<br>Temperature                            | 115°C option selected <sup>(5)</sup>                                                                                                                                                              | 115 |       |       | °C      |

| DETECTION AN           | ND TIMING <sup>(5)</sup>                                     |                                                                                                                                                                                                   |     |       |       |         |

| V <sub>VBUSDET</sub>   | VBUS Detection Threshold                                     |                                                                                                                                                                                                   | 3.5 | 3     | 4     | V       |

| Т <sub>РОК</sub>       | Power OK Debounce Time                                       | $V_{VBUS} > V_{VBAT} + V_{OK_CHG}$                                                                                                                                                                | 30  |       |       |         |

| T <sub>PRE_FULL</sub>  | Debounce Time from Pre-<br>Charge to Full-rate<br>Transition | Pre-charge to full-rate charging transition                                                                                                                                                       | 55  |       |       | ms      |

| T <sub>EOC</sub>       | Debounce Time from CV to<br>End-of-Charge Transition         |                                                                                                                                                                                                   | 400 |       |       | ms      |

| T <sub>CHG</sub>       | Charge Safety Timer                                          | Pre-charge Mode                                                                                                                                                                                   | 45  |       |       | minutes |

(1) Junction-to-ambient thermal resistance is highly application and board layout dependent. In applications where high power dissipation exists, special care must be given to thermal dissipation issues in board design.

(2) Dropout voltage is the voltage difference between the input and the output at which the output voltage drops to 100 mV below its nominal value.

The parameters in the electrical characteristic table are tested under open loop conditions at V<sub>bat</sub> = 3.7 unless otherwise specified. For (3) performance over the input voltage range and closed loop condition, refer to the datasheet curves. The minimum input voltage equals  $V_{OUT}$  (nom) + 0.5V or 2.5V, which ever is greater.

(4)

Min and Max limits are specified by design, test or statistical analysis. Typical numbers are not ensured, but do represent the most likely (5) norm.

### LP8727 Control Registers

| ADDR | REGISTER            | POR<br>DEFAULT | BIT7    | BIT6          | BIT5         | BIT4    | BIT3   | BIT2     | BIT1    | BIT0            |     |  |

|------|---------------------|----------------|---------|---------------|--------------|---------|--------|----------|---------|-----------------|-----|--|

| 0x00 | DEVICE ID           | 0011xxxx       |         | VENDO         | or id        |         |        | CHI      | P_REV   |                 |     |  |

| 0x01 | CONTROL1            | x0000001       | RESV'D  | ID_2P2        | ID_620       | ID_200  | VLDO   | SEMREN   | ADC_EN  | CP_EN           |     |  |

| 0x02 | CONTROL2            | 0000xx01       | INTPOL  | INT_EN        | MIC_LP       | CP_AUD  | RESV'D | RESV'D   | CHG_TYP | USB_DET_<br>DIS |     |  |

| 0x03 | SW<br>CONTROL       | x0000000       | RESV'D  | MIC_ON        |              | DP2     |        | DP2      |         |                 | DM1 |  |

| 0x04 | INT_STAT1           | 00000000       | CHGDET  | MR_<br>COMP   | SEND/E<br>ND | VBUS    | IDNO   |          |         |                 |     |  |

| 0x05 | INT_STAT2           | 00000000       | CHG     | TSHD          | TMP          | OVLO    | UVLO   | RESV'D   | RESV'D  | RESV'D          |     |  |

| 0x06 | STATUS1             | 00000000       | DCPORT  | CHPORT        | CHG          | _STAT   | RESV'D | RESV'D   | RESV'D  | C1COMP          |     |  |

| 0x07 | STATUS2             | 00000000       | т       | MP_STAT       |              | RESV'D  | RESV'D | RESV'D   | RESV'D  | RESV'D          |     |  |

| 0x08 | CHARGER<br>CONTROL1 | 010010xx       | CHG_EN  | EXPDET<br>_EN | PTM          | CHG_OFF | IPRE   | CHG      | RESV'D  | RESV'D          |     |  |

| 0x09 | CHARGER<br>CONTROL2 | 0010x001       | CHG_SET |               |              | RESV'D  |        | IMIN_SET |         |                 |     |  |

# I<sup>2</sup>C-Compatible Slave Address: 7'h27<sup>(6)</sup>

(6) (**Bolded** locations are Read-Only Bits.) Resv'd = Reserved SNVS898A-OCTOBER 2012-REVISED MAY 2013

www.ti.com

# DETAILED REGISTER DESCRIPTIONS<sup>(1)</sup>

| ADDR | REGISTER<br>NAME | BIT NAME  | BIT   | POR DEFAULT | DESCRIPTION                                                                                                                            |

|------|------------------|-----------|-------|-------------|----------------------------------------------------------------------------------------------------------------------------------------|

| 0x00 | DEVICE ID        | CHIP_REV  | [3:0] | xxxx        | Chip revision.                                                                                                                         |

| 0000 | DEVICE ID        | VENDOR ID | [7:4] | 0011        | Texas Instruments vendor ID.                                                                                                           |

|      |                  |           |       |             | Enable charge pump for analog switch operation.                                                                                        |

|      |                  | CP_EN     | 0     | 1           | When CP_EN = 0, input signals to the analog switches should not go below GND.                                                          |

|      |                  |           |       |             | 0: Disable                                                                                                                             |

|      |                  |           |       |             | 1: Enable                                                                                                                              |

|      |                  |           |       |             | Enable ID detection LDO and internal ADC.                                                                                              |

|      |                  | ADC_EN    | 1     | 0           | 0: Disable                                                                                                                             |

|      |                  |           |       |             | 1: Enable                                                                                                                              |

|      |                  |           |       |             | Enable ID detection LDO and SEND/END & MR comparators.                                                                                 |

|      |                  | SEMREN    | 2     | 0           | 0: Disable                                                                                                                             |

|      |                  |           |       |             | 1: Enable                                                                                                                              |

|      |                  |           |       |             | ID detection LDO voltage setting.                                                                                                      |

|      |                  | VLDO      | 3     | 0           | 0: 2.3V                                                                                                                                |

| 0x01 | CONTROL1         |           |       |             | 1: 2.6V                                                                                                                                |

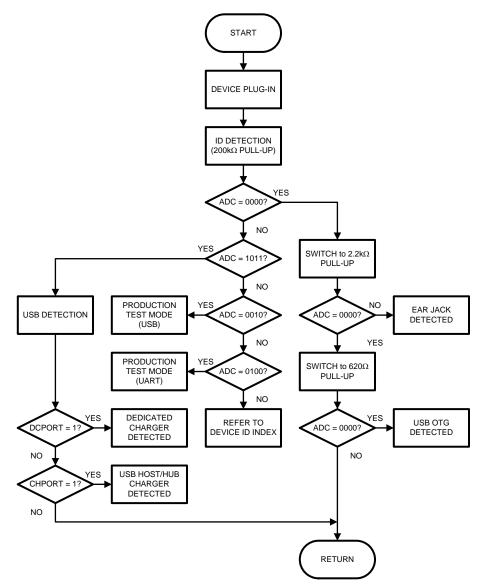

|      |                  |           |       |             | Connect ID detection LDO to ID pin through an internal 200 $k\Omega$ resistor.                                                         |

|      |                  | ID_200    | 4     | 0           | 0: Disable                                                                                                                             |

|      |                  |           |       |             | 1: Enable                                                                                                                              |

|      |                  |           |       |             | Connect ID detection LDO to ID pin through an internal $620\Omega$ resistor.                                                           |

|      |                  | ID_620    | 5     | 0           | 0: Disable                                                                                                                             |

|      |                  |           |       |             | 1: Enable                                                                                                                              |

|      |                  | ID_2P2    | 6     | 0           | Connect ID detection LDO to RES output for microphone biasing. A 2.2 k $\Omega$ external resistor is required between RES and ID pins. |

|      |                  |           | Ŭ     | , v         | 0: Disable                                                                                                                             |

|      |                  |           |       |             | 1: Enable                                                                                                                              |

|      |                  | RESERVED  | 7     | х           | Not used.                                                                                                                              |

LP8727

| USB_DET_DIS 0 1 Disable USB charger detection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| 1: Disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                        |

| CHG_TYP 1 0 Enable charger type detection.<br>0: Disable<br>1: Enable<br>1: Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                        |

| Enable internal 100Ω pull-down<br>AUD2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | resistors on AUD1 and  |

| 0: Disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                        |

| 0x02 CONTROL2 1: Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                        |

| Enable microphone low-power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | mode.                  |

| MIC_LP 5 0 0: Disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                        |

| 1: Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                        |

| Enable interrupt output. When one wasked and pending interrupt output inte |                        |

| INT_EN 6 0 0: Disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                        |

| 1: Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                        |