DS90UH928Q-Q1

SNLS440C - MARCH 2013 - REVISED JULY 2016

# DS90UH928Q-Q1 5 MHz to 85 MHz 24-bit Color FPD-Link III to FPD-Link Deserializer With **HDCP**

### **Features**

- Qualified for Automotive Applications AEC-Q100

- Device Temperature Grade 2: -40°C to +105°C Ambient Operating Temperature Range

- Device HBM ESD Classification Level ±8 kV

- Device CDM ESD Classification Level C6

- Integrated HDCP Cipher Engine with On-Chip Key Storage

- Supports HDCP Repeater Application

- Bidirectional Control Channel Interface with I<sup>2</sup>C Compatible Serial Control Bus

- Low EMI FPD-Link Video Output

- Supports High Definition (720p) Digital Video

- RGB888 + VS, HS, DE and I2S Audio Supported

- 5 MHz to 85 MHz Pixel Clock Support

- Up to 4 I2S Digital Audio Outputs for Surround Sound Applications

- 4 Bidirectional GPIO Channels with 2 Dedicated

- Single 3.3 V supply with 1.8 V or 3.3 V Compatible LVCMOS I/O Interface

- AC-Coupled STP Interconnect Up to 10 Meters

- DC-Balanced and Scrambled Data with Embedded Clock

- Adaptive Cable Equalization

- Image Enhancement (White Balance & Dithering) and Internal Pattern Generation

- **Backward Compatible Modes**

## **Applications**

- Automotive Displays for Navigation

- Rear Seat Entertainment Systems

## Description

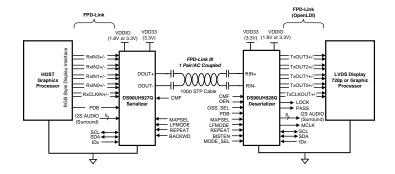

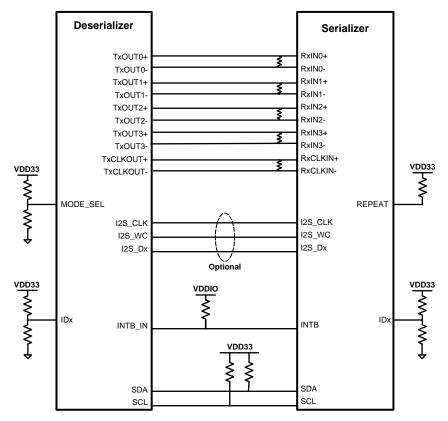

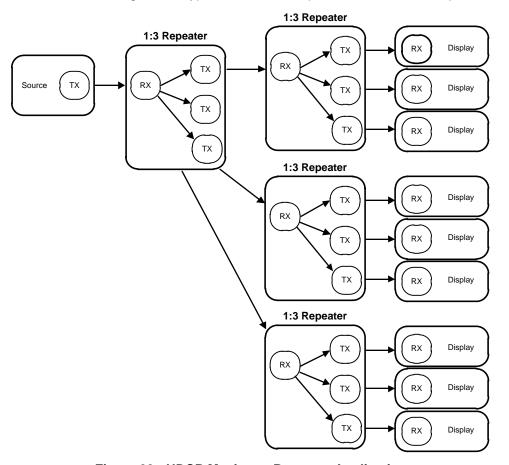

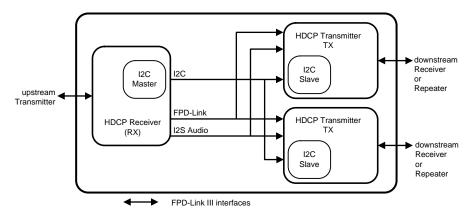

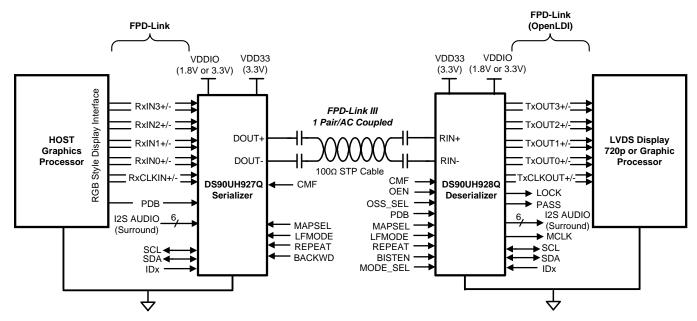

The DS90UH928Q-Q1 deserializer, in conjunction with a DS90UH925Q-Q1 or DS90UH927Q-Q1 serializer, provides a solution for secure distribution of content-protected digital video and audio within automotive infotainment systems. The converts a high-speed serialized interface with an embedded clock, delivered over a single signal pair (FPD-Link III), to four LVDS data/control streams, one LVDS clock pair (OpenLDI (FPD-Link)), and I2S audio data. The digital video and audio data is protected using the industry standard HDCP copy protection scheme. The serial bus scheme, FPD-Link supports high-speed forward channel data transmission and low-speed full duplex back channel communication over a single differential link. Consolidation of audio, video data and control over a single differential pair reduces the interconnect size and weight, while also eliminating skew issues and simplifying system design.

Adaptive input equalization of the serial input stream provides compensation for transmission medium losses and deterministic jitter. EMI is minimized by the use of low voltage differential signaling.

The HDCP cipher engine is implemented in both the serializer and deserializer. HDCP keys are stored in on-chip memory.

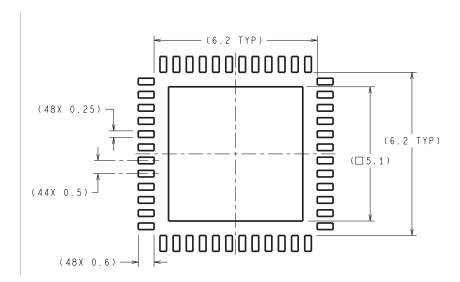

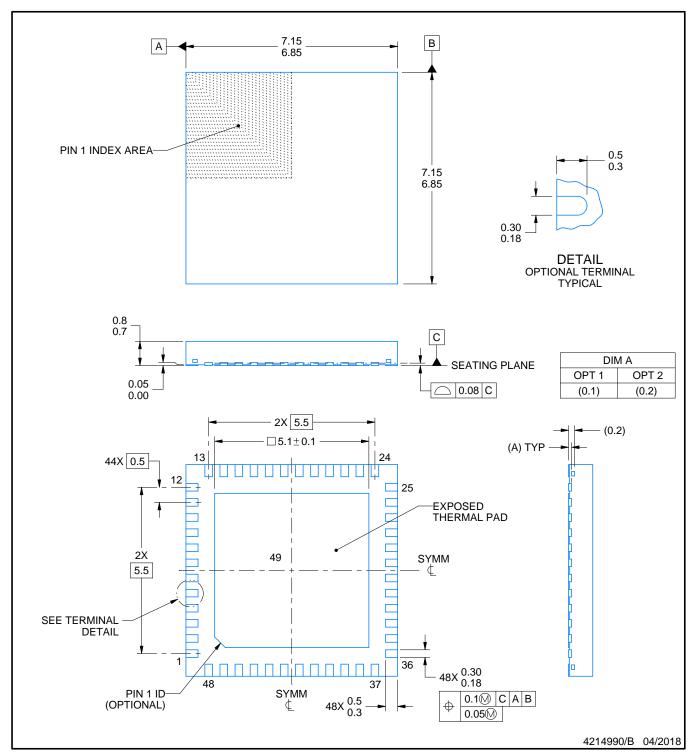

## Device Information<sup>(1)</sup>

| PART NUMBER   | PACKAGE   | BODY SIZE (NOM)   |

|---------------|-----------|-------------------|

| DS90UH928Q-Q1 | WQFN (48) | 7.00 mm × 7.00 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

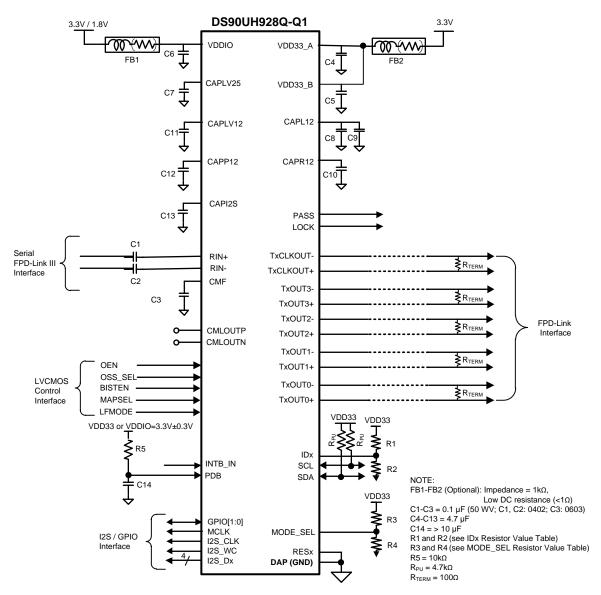

# 4 Application Diagram

# **Table of Contents**

| 1 | Features 1                                            |    | 8.4 Device Functional Modes                         | 31   |

|---|-------------------------------------------------------|----|-----------------------------------------------------|------|

| 2 | Applications 1                                        |    | 8.5 Programming                                     | 36   |

| 3 | Description 1                                         |    | 8.6 Register Maps                                   | 38   |

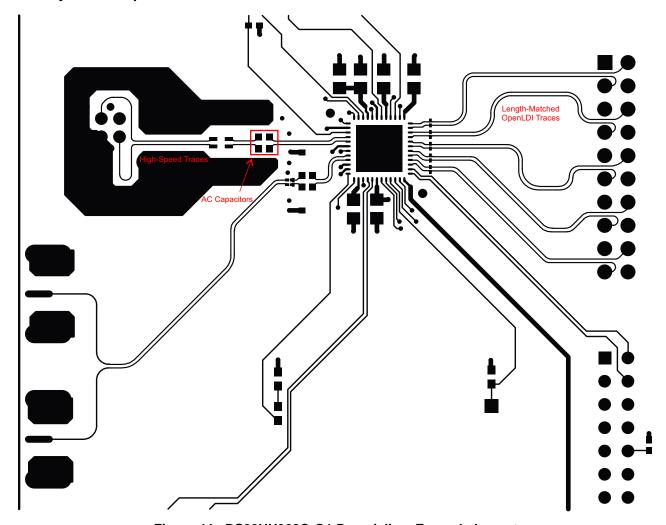

| 4 | Application Diagram1                                  | 9  | Application and Implementation                      | 55   |

| 5 | Revision History2                                     |    | 9.1 Application Information                         | 55   |

| 6 | Pin Configuration and Functions 4                     |    | 9.2 Typical Application                             | 55   |

| 7 | _                                                     |    | 9.3 AV Mute Prevention                              | 58   |

| ′ | Specifications                                        |    | 9.4 OEN Toggling Limitation                         | 58   |

|   | 7.1 Absolute Maximum Ratings                          | 10 | Power Supply Recommendations                        | . 58 |

|   | 7.2 ESD Ratings                                       |    | 10.1 Power Up Requirements and PDB Pin              | 58   |

|   | 7.3 Recommended Operating Conditions                  | 11 | Layout                                              |      |

|   |                                                       |    | 11.1 Layout Guidelines                              |      |

|   | 7.5 DC Electrical Characteristics                     |    | 11.2 Layout Example                                 |      |

|   | 7.6 AC Electrical Characteristics                     | 12 | Device and Documentation Support                    |      |

|   | 7.7 Timing Requirements for the Serial Control Bus 12 |    | 12.1 Documentation Support                          |      |

|   | 7.8 Timing Requirements                               |    | 12.2 Receiving Notification of Documentation Update |      |

|   | 7.9 DC and AC Serial Control Bus Characteristics 13   |    | 12.3 Community Resources                            |      |

| _ | 7.10 Typical Characteristics                          |    | 12.4 Trademarks                                     |      |

| 8 | Detailed Description                                  |    | 12.5 Electrostatic Discharge Caution                |      |

|   | 8.1 Overview                                          |    | 12.6 Glossary                                       |      |

|   | 8.2 Functional Block Diagram                          | 13 | Mechanical, Packaging, and Orderable                | 00   |

|   | 8.3 Feature Description                               | 13 | Information                                         | 63   |

|   |                                                       |    |                                                     |      |

# **5 Revision History**

| Changes from Revision B (January 2015) to Revision C | Page |

|------------------------------------------------------|------|

| Added "OpenLDI".                                     | 1    |

| Added AV Mute Prevention section.                    | 2    |

| Added OEN Toggling Limitation.                       | 2    |

| Changed the shared function.                         | 4    |

| Added the shared function                            | 5    |

| Changed Pin name                                     | 11   |

| Added Input Jitter specification.                    | 11   |

| Added I2S Set-up Time.                               | 12   |

| Added I2S Hold Time.                                 | 12   |

| Added Read Register at the first step.               | 26   |

| Changed the updated GPIO Configuration table.        | 27   |

| Changed to one tenth of Resistor value               | 33   |

| Changed and swapped IDEAL RATIO and IDEAL VR2 values | 37   |

| Changed to one tenth of Resistor value               | 37   |

| Changed and Revised data to 0x01                     | 43   |

| Changed and revised GPIO Direction description.      | 45   |

| Changed and revised Register Type to RW from R.      | 46   |

| Added and disclosed Link Error Count Register.       | 49   |

| Added and disclosed LVDS Setting Register.           | 50   |

| Changed and revised Register Address.                | 52   |

| Added AV Mute Prevention section.                    | 58   |

| Added OEN Toggling Limitation.                       | 58   |

| Changed and updated Power-Up Requirements and PDB    |      |

| ·                                                    |      |

## **Revision History (continued)**

## Changes from Revision A (April 2013) to Revision B

**Page**

Added ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and

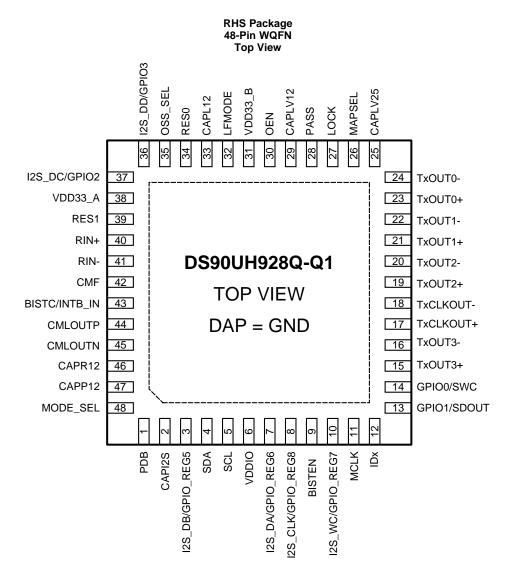

## 6 Pin Configuration and Functions

**Pin Functions**

| Pi          | IN                | I/O, TYPE                 |                                                                                                                        |

|-------------|-------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------|

| NAME        | AME NO.           |                           | DESCRIPTION                                                                                                            |

| FPD-LINK OU | TPUT INTERF       | ACE                       |                                                                                                                        |

| TxCLKOUT-   | 18                | O, LVDS                   | Inverting LVDS Clock Output The pair requires external 100 $\Omega$ differential termination for standard LVDS levels  |

| TxCLKOUT+   | 17                | O, LVDS                   | True LVDS Clock Output The pair requires external 100 $\Omega$ differential termination for standard LVDS levels       |

| TxOUT[3:0]- | 16, 20, 22,<br>24 | O, LVDS                   | Inverting LVDS Data Outputs Each pair requires external 100 $\Omega$ differential termination for standard LVDS levels |

| TxOUT[3:0]+ | 15, 19, 21,<br>23 | O, LVDS                   | True LVDS Data Outputs Each pair requires external 100 $\Omega$ differential termination for standard LVDS levels      |

| LVCMOS INTE | ERFACE            |                           |                                                                                                                        |

| GPIO[1:0]   | 13, 14            | I/O, LVCMOS with pulldown | · ·                                                                                                                    |

| GPIO[3:2]   | 36, 37            | I/O, LVCMOS with pulldown | · ·                                                                                                                    |

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

# Pin Functions (continued)

| PIN                                      |                    |                            |                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|------------------------------------------|--------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME                                     | NO.                | I/O, TYPE                  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| GPIO_REG[8<br>:5]                        | 8, 10, 7, 3        | I/O, LVCMOS with pulldown  | General Purpose I/O, register access only<br>Shared with I2S_CLK, I2S_WC, I2S_DA, I2S_DB                                                                                                                                                                                                                                                                                                                                   |  |  |

| 12\$_DA<br>12\$_DB<br>12\$_DC<br>12\$_DD | 7<br>3<br>37<br>36 | O, LVCMOS                  | Digital Audio Interface I2S Data Outputs Shared with GPIO_REG6, GPIO_REG5, GPIO2, GPIO3                                                                                                                                                                                                                                                                                                                                    |  |  |

| INTB_IN                                  | 43                 | I, LVCMOS with pulldown    | HDCP Interrupt Input<br>Shared with BISTC                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

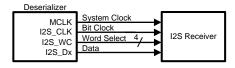

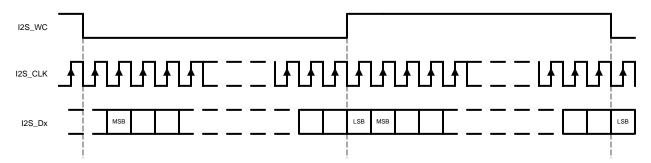

| MCLK<br>I2S_WC<br>I2S_CLK                | 11<br>10<br>8      | O, LVCMOS                  | Digital Audio Interface I2S Master Clock, Word Clock and I2S Bit Clock Outputs I2S_WC and I2S_CLK are shared with GPIO_REG7 and GPIO_REG8                                                                                                                                                                                                                                                                                  |  |  |

| SDOUT<br>SWC                             | 13, 14             | I/O, LVCMOS with pulldown  | Auxiliary Digital Audio Interface I2S Data Output and Word Clock<br>Shared with GPIO1 and GPIO0                                                                                                                                                                                                                                                                                                                            |  |  |

| CONTROL AN                               | D CONFIGURA        | ATION                      |                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| BISTC                                    | 43                 | I, LVCMOS<br>with pulldown | BIST Clock Select Shared with INTB_IN Requires a 10 k $\Omega$ pullup if set HIGH                                                                                                                                                                                                                                                                                                                                          |  |  |

| BISTEN                                   | 9                  | I, LVCMOS with pulldown    | BIST Enable Requires a 10 $k\Omega$ pullup if set HIGH                                                                                                                                                                                                                                                                                                                                                                     |  |  |

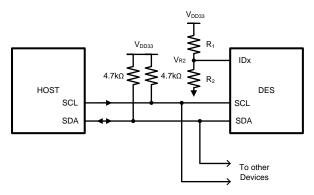

| IDx                                      | 12                 | I, Analog                  | I2C Address Select External pullup to $V_{DD33}$ is required under all conditions. <b>DO NOT FLOAT.</b> Connect to external pullup to $V_{DD33}$ and pulldown to GND to create a voltage divider. See Table 7                                                                                                                                                                                                              |  |  |

| LFMODE                                   | 32                 | I, LVCMOS with pulldown    | Low Frequency Mode Select LFMODE = 0, 15 MHz $\leq$ TxCLKOUT $\leq$ 85 MHz (Default) LFMODE = 1, 5 MHz $\leq$ TxCLKOUT $<$ 15 MHz Requires a 10 k $\Omega$ pullup if set HIGH                                                                                                                                                                                                                                              |  |  |

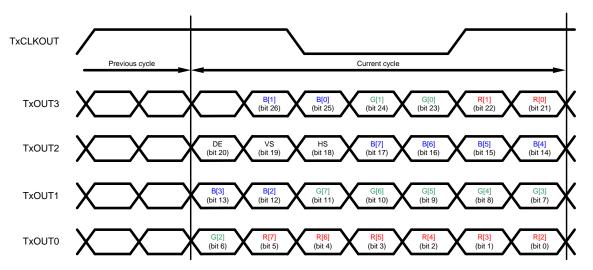

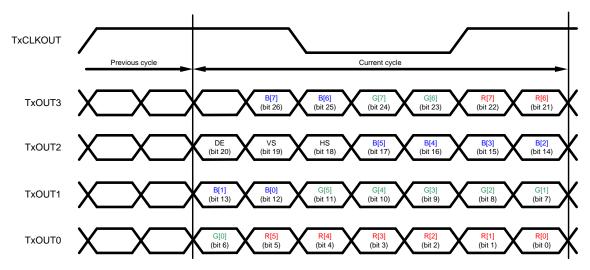

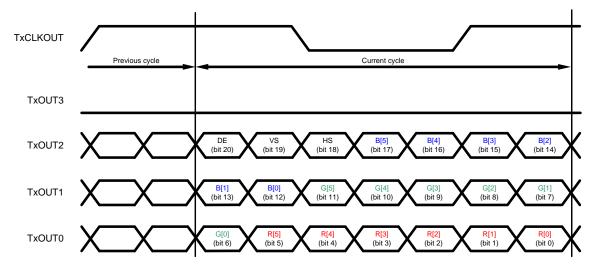

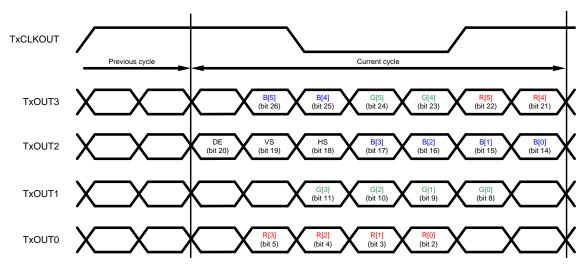

| MAPSEL                                   | 26                 | I, LVCMOS<br>with pulldown | FPD-Link Output Map Select MAPSEL = 0, LSBs on TxOUT3± (Default) MAPSEL = 1, MSBs on TxOUT3± Requires a 10 kΩ pullup if set HIGH                                                                                                                                                                                                                                                                                           |  |  |

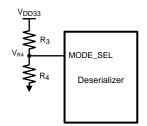

| MODE_SEL                                 | 48                 | I, Analog                  | Device Configuration Select Configures Backwards Compatibility (BKWD), Repeater (REPEAT), I2S 4-channel (I2S_B), and Long Cable (LCBL) modes Connect to external pullup to V <sub>DD33</sub> and pulldown to GND resistors to create a voltage divider. <b>DO NOT FLOAT</b> See Table 6                                                                                                                                    |  |  |

| OEN                                      | 30                 | I, LVCMOS<br>with pulldown | Output Enable Requires a 10 k $\Omega$ pullup if set HIGH See Table 5                                                                                                                                                                                                                                                                                                                                                      |  |  |

| OSS_SEL                                  | 35                 | I, LVCMOS<br>with pulldown | Output Sleep State Select Requires a 10 k $\Omega$ pullup if set HIGH See Table 5                                                                                                                                                                                                                                                                                                                                          |  |  |

| PDB                                      | 1                  | I, LVCMOS                  | Power-down Mode Input Pin Must be driven or pulled up to $V_{DD33}$ . Refer to <i>Power Up Requirements and PDB Pin</i> Power Up Requirements and PDB Pin in . PDB = H, device is enabled (normal operation) PDB = L, device is powered down When the device is in the powered down state, the LVDS and LVCMOS outputs are tri-state, the PLL is shutdown, and $I_{DD}$ is minimized. Control Registers are <b>RESET</b> . |  |  |

| SCL                                      | 5                  | I/O, Open<br>Drain         | $\rm I^2C$ Clock Input/Output Interface Must have an external pullup to $\rm V_{DD33}.$ DO NOT FLOAT Recommended pullup: 4.7 $\rm k\Omega$                                                                                                                                                                                                                                                                                 |  |  |

| SDA                                      | 4                  | I/O, Open<br>Drain         | I2C Data Input/Output Interface Must have an external pullup to $V_{DD33}$ . <b>DO NOT FLOAT</b> Recommended pullup: 4.7 k $\Omega$                                                                                                                                                                                                                                                                                        |  |  |

| STATUS                                   |                    |                            |                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

# Pin Functions (continued)

| Р                                                | IN                        |           |                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------------|---------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                             | NO.                       | I/O, TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                     |

| LOCK                                             | 27                        | O, LVCMOS | LOCK Status Output 0: PLL is unlocked, I2S, GPIO, TxOUT[3:0]±, and TxCLKOUT± are idle with output states controlled by OEN and OSS_SEL. May be used to indicate Link Status or Display Enable. 1: PLL is locked, outputs are active with output states controlled by OEN and OSS_SEL Route to test point or pad (Recommended). Float if unused. |

| PASS                                             | 28                        | O, LVCMOS | PASS Status Output 0: One or more errors were detected in the received BIST payload (BIST Mode) 1: Error-free transmission (BIST Mode) Route to test point or pad (Recommended). Float if unused.                                                                                                                                               |

| FPD-LINK III S                                   | SERIAL INTER              | FACE      |                                                                                                                                                                                                                                                                                                                                                 |

| CMF                                              | 42                        | Analog    | Common Mode Filter Requires a 0.1 µF capacitor to GND                                                                                                                                                                                                                                                                                           |

| CMLOUTN                                          | 45                        | O, LVDS   | Inverting Loop-through Driver Output Monitor point for equalized forward channel differential signal. Connect a 100 $\Omega$ resistor between CMLOUTN and CMLOUTP pins to monitor.                                                                                                                                                              |

| CMLOUTP                                          | 44                        | O, LVDS   | True Loop-through Driver Output Monitor point for equalized forward channel differential signal. Connect a 100 $\Omega$ resistor between CMLOUTN and CMLOUTP pins to monitor.                                                                                                                                                                   |

| RIN-                                             | 41                        | I/O, LVDS | FPD-Link III Inverting Input The output must be AC-coupled with a 0.1 $\mu$ F capacitor. This pin has 100 $\Omega$ (typ.) internal termination between RIN- and RIN+ pins.                                                                                                                                                                      |

| RIN+                                             | 40                        | I/O, LVDS | FPD-Link III True Input The output must be AC-coupled with a 0.1 $\mu$ F capacitor. This pin has 100 $\Omega$ (typ.) internal termination between RIN- and RIN+ pins.                                                                                                                                                                           |

| POWER AND                                        | GROUND <sup>(1)</sup>     | *         |                                                                                                                                                                                                                                                                                                                                                 |

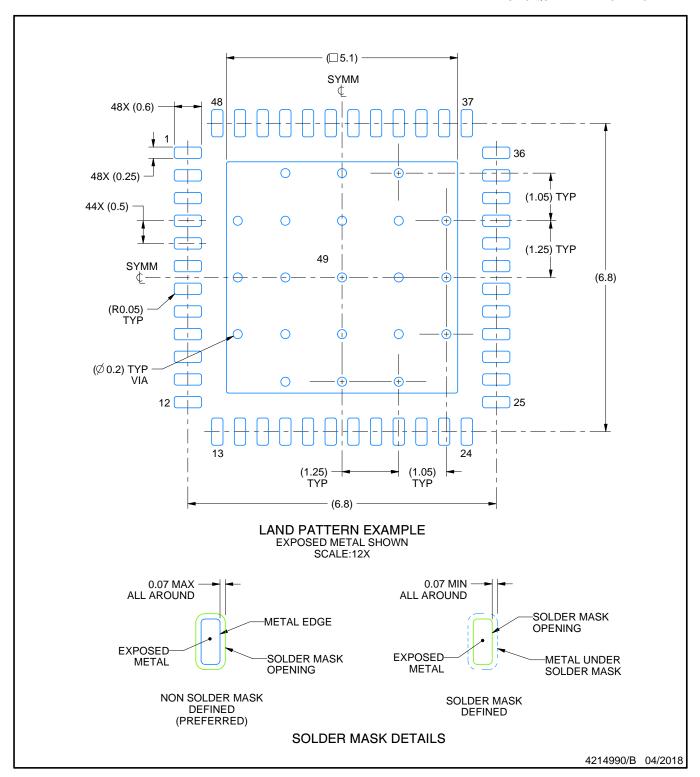

| GND                                              | DAP                       | Ground    | Large metal contact at the bottom center of the device package Connect to the ground plane (GND) with at least 9 vias                                                                                                                                                                                                                           |

| VDD33_A<br>VDD33_B                               | 38<br>31                  | Power     | 3.3 V Power to on-chip regulator Each pin requires a 4.7 µF capacitor to GND                                                                                                                                                                                                                                                                    |

| VDDIO                                            | 6                         | Power     | 1.8 V/3.3 V LVCMOS I/O Power<br>Requires a 4.7 µF capacitor to GND                                                                                                                                                                                                                                                                              |

| REGULATOR                                        | CAPACITOR                 |           |                                                                                                                                                                                                                                                                                                                                                 |

| CAPI2S<br>CAPLV25<br>CAPLV12<br>CAPR12<br>CAPP12 | 2<br>25<br>29<br>46<br>47 | CAP       | Decoupling capacitor connection for on-chip regulator Each requires a 4.7 μF decoupling capacitor to GND                                                                                                                                                                                                                                        |

| CAPL12                                           | 33                        | CAP       | Decoupling capacitor connection for on-chip regulator Requires two 4.7 μF decoupling capacitors to GND                                                                                                                                                                                                                                          |

| OTHER                                            | 1                         |           |                                                                                                                                                                                                                                                                                                                                                 |

| RES[1:0]                                         | 39, 34                    | GND       | Reserved<br>Connect to GND                                                                                                                                                                                                                                                                                                                      |

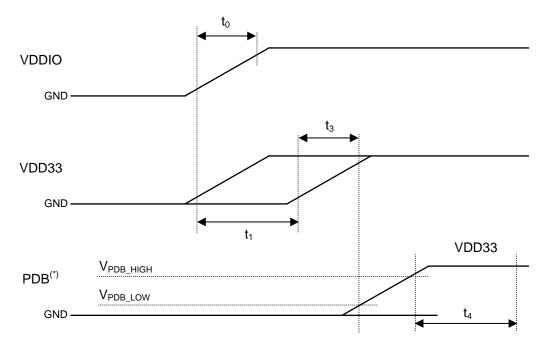

<sup>(1)</sup> The  $V_{DD}$  ( $V_{DD33}$  and  $V_{DDIO}$ ) supply ramp should be faster than 1.5 ms with a monotonic rise.

## 7 Specifications

# 7.1 Absolute Maximum Ratings<sup>(1)</sup> (2)

|                                                   | MIN  | MAX                       | UNIT |

|---------------------------------------------------|------|---------------------------|------|

| Supply Voltage – V <sub>DD33</sub> <sup>(3)</sup> | -0.3 | 4                         | ٧    |

| Supply Voltage – V <sub>DDIO</sub> <sup>(3)</sup> | -0.3 | 4                         | V    |

| LVCMOS I/O Voltage                                | -0.3 | (V <sub>DDIO</sub> + 0.3) | V    |

| Deserializer Input Voltage                        | -0.3 | 2.75                      | V    |

| Junction Temperature                              |      | 150                       | °C   |

| Storage temperature, T <sub>stg</sub>             | -65  | 150                       | °C   |

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

For soldering specifications, see product folder at www.ti.com and SNOA549.

## 7.2 ESD Ratings

|                    |               |                                                            |                                             | VALUE  | UNIT      |

|--------------------|---------------|------------------------------------------------------------|---------------------------------------------|--------|-----------|

|                    |               | Human body model (HBM), pe                                 | er AEC Q100-002, all pins <sup>(1)</sup>    | ±8000  | V         |

| V <sub>(ESD)</sub> |               | Charged device model (CDM)                                 | , per AEC Q100-011, all pins                | ±1250  | V         |

|                    |               | Machine model (MM)                                         |                                             | ±250   | V         |

|                    |               | (IEC, powered-up only)                                     | Air Discharge (Pins 40, 41, 44, and 45)     | ±15000 | V         |

|                    | Electrostatic | $R_D = 330 \Omega, C_S = 150 pF$                           | Contact Discharge (Pins 40, 41, 44, and 45) | ±8000  | V V V V V |

| (202)              | discharge     | (ISO10605)                                                 | Air Discharge (Pins 40, 41, 44, and 45)     | ±15000 |           |

|                    |               | $R_D = 330 \ \Omega, C_S = 150 \ pF$                       | Contact Discharge (Pins 40, 41, 44, and 45) | ±8000  | V         |

|                    |               | (ISO10605)                                                 | Air Discharge (Pins 40, 41, 44, and 45)     | ±15000 | V         |

|                    |               | $R_D = 2 \text{ k}\Omega, C_S = 150 \text{ pF or} $ 330 pF | Contact Discharge (Pins 40, 41, 44, and 45) | ±8000  | V         |

<sup>(1)</sup> AEC Q100-002 indicates HBM stressing is done in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

## 7.3 Recommended Operating Conditions

|                                                               |                                                      | MIN  | NOM | MAX  | UNIT       |

|---------------------------------------------------------------|------------------------------------------------------|------|-----|------|------------|

| Supply Voltage (V <sub>DD33</sub> ) <sup>(1)</sup>            |                                                      | 3    | 3.3 | 3.6  | V          |

| LVCMOS Supply Voltage (V <sub>DDIO</sub> ) <sup>(1)</sup> (2) | Connect V <sub>DDIO</sub> to 3.3 V and use 3.3 V IOs | 3    | 3.3 | 3.6  | V          |

|                                                               | Connect V <sub>DDIO</sub> to 1.8 V and use 1.8 V IOs | 1.71 | 1.8 | 1.89 | >          |

| Operating Free Air<br>Temperature (T <sub>A</sub> )           |                                                      | -40  | 25  | 105  | °C         |

| PCLK Frequency (out of TxCLKOUT±)                             |                                                      | 5    |     | 85   | MHz        |

| Supply Noise (3)                                              |                                                      |      |     | 100  | $mV_{P-P}$ |

$<sup>(1) \</sup>quad \text{The DS90UH928Q-Q1V}_{DD33} \text{ and V}_{DDIO} \text{ voltages require a specific ramp rate during power up. The power supply ramp time must be}$ less than 1.5 ms with a monotonic rise.

The DS90UH928Q-Q1V<sub>DD33</sub> and V<sub>DDIO</sub> voltages require a specific ramp rate during power up. The power supply ramp time must be less than 1.5 ms with a monotonic rise.

$V_{DDIO}$  should not exceed  $V_{DD33}$  by more than 300 mV ( $V_{DDIO} < V_{DD33} + 0.3 \text{ V}$ ). Supply noise testing was done with minimum capacitors on the PCB. A sinusoidal signal is AC-coupled to the  $V_{DD33}$  and  $V_{DDIO}$  supplies with amplitude >100 mVp-p measured at the device VDD33 and VDDIO pins. Bit error rate testing of input to the Ser and output of the Des with 10 meter cable shows no error when the noise frequency on the Ser is less than 50 MHz. The Des on the other hand shows no error when the noise frequency is less than 50 MHz.

## 7.4 Thermal Information

|                        |                                              | DS90UH928Q-Q1 |      |

|------------------------|----------------------------------------------|---------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | RHS (WQFN)    | UNIT |

|                        |                                              | 48 PINS       |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 26.4          | °C/W |

| $R_{\theta JC(top)}$   | Junction-to-case (top) thermal resistance    | 4.4           | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 4.3           | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter   | 0.1           | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 4.3           | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | 0.8           | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 7.5 DC Electrical Characteristics

Over recommended operating supply and temperature ranges unless otherwise specified. (1) (2) (3)

|                 | PARAMETER                    | TEST CONDITIONS                                                     | PIN/FREQ.                             | MIN | TYP | MAX        | UNIT |

|-----------------|------------------------------|---------------------------------------------------------------------|---------------------------------------|-----|-----|------------|------|

| 3.3 V LV        | CMOS I/O                     |                                                                     |                                       |     |     |            |      |

| V <sub>IH</sub> | High Level Input Voltage     | V 20V to 26V                                                        | GPIO[3:0],                            | 2.0 |     | $V_{DDIO}$ | V    |

| V <sub>IL</sub> | Low Level Input Voltage      | $V_{\rm DDIO} = 3.0 \text{ V to } 3.6 \text{ V}$                    | REG_GPIO[8:<br>5], LFMODE,            | GND |     | 0.8        | V    |

| I <sub>IN</sub> | Input Current                | V <sub>IN</sub> = 0 V or V <sub>IN</sub> = 3.0 V to 3.6 V           | MAPSEL,<br>BISTEN,                    | -10 | ±1  | +10        | μА   |

| V <sub>IH</sub> | High Level Input Voltage     |                                                                     |                                       | 2.0 |     | $V_{DDIO}$ | V    |

| V <sub>IL</sub> | Low Level Input Voltage      |                                                                     | (4)PDB                                | GND |     | 0.7        | V    |

| I <sub>IN</sub> | Input Current                | $V_{IN} = 0 \text{ V or } V_{IN} = 3.0 \text{ V to } 3.6 \text{ V}$ |                                       | -10 | ±1  | +10        | μΑ   |

| V <sub>OH</sub> | HIGH Level Output Voltage    | I <sub>OH</sub> = -4 mA                                             | GPIO[3:0],                            | 2.4 |     | $V_{DDIO}$ | V    |

| V <sub>OL</sub> | LOW Level Output Voltage     | $I_{OL} = +4 \text{ mA}$                                            | REG_GPIO[8:<br>5], MCLK,              | 0   |     | 0.4        | V    |

| I <sub>OS</sub> | Output Short Circuit Current | V <sub>OUT</sub> = 0 V <sup>(5)</sup>                               | I2S_WC,                               |     | -55 |            | mA   |

| I <sub>OZ</sub> | Tri-state Output Current     | V <sub>OUT</sub> = 0 V or V <sub>DDIO</sub> , PDB = L               | I2S_CLK,<br>I2S_D[A:D],<br>LOCK, PASS | -20 |     | +20        | μΑ   |

<sup>(1)</sup> The Electrical Characteristics tables list ensured specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics conditions and/or notes. Typical specifications are estimations only and are not ensured.

Typical values represent most likely parametric norms at  $V_{DD33} = 3.3 \text{ V}$ ,  $V_{DDIO} = 1.8 \text{ V}$  or 3.3 V,  $T_A = 25 ^{\circ}\text{C}$ , and at the Recommended Operating Conditions at the time of product characterization and are not ensured.

Current into device pins is defined as positive. Current out of a device pin is defined as negative. Voltages are referenced to ground except  $V_{OD}$  and  $\Delta V_{OD}$ , which are differential voltages.

PDB is specified to 3.3 V LVCMOS only and must be driven or pulled up to  $V_{DD33}$  or to  $V_{DDIO} \ge 3.0 \text{ V}$ .  $I_{OS}$  is not specified for an indefinite period of time. Do not hold in short circuit for more than 500 ms or part damage may result.

# **DC Electrical Characteristics (continued)**

Over recommended operating supply and temperature ranges unless otherwise specified. (1) (2) (3)

|                    | PARAMETER                                      | TEST CONDITIONS                                                              | PIN/FREQ.                             | MIN                         | TYP  | MAX                         | UNIT |

|--------------------|------------------------------------------------|------------------------------------------------------------------------------|---------------------------------------|-----------------------------|------|-----------------------------|------|

| 1.8 V LVC          | MOS I/O                                        |                                                                              |                                       |                             |      |                             |      |

| V <sub>IH</sub>    | High Level Input Voltage                       | V = 1.71 V to 1.80 V                                                         | GPIO[3:0],<br>REG_GPIO[8:             | 0.65 *<br>V <sub>DDIO</sub> |      | $V_{DDIO}$                  | ٧    |

| V <sub>IL</sub>    | Low Level Input Voltage                        | V <sub>DDIO</sub> = 1.71 V to 1.89 V                                         | 5], LFMODE,<br>MAPSEL,<br>BISTEN,     | 0                           |      | 0.35 *<br>V <sub>DDIO</sub> | V    |

| I <sub>IN</sub>    | Input Current                                  | V <sub>IN</sub> = 0 V or V <sub>IN</sub> = 1.71 V to 1.89 V                  | BISTC,<br>INTB_IN,<br>OEN,<br>OSS_SEL | -10                         |      | 10                          | μΑ   |

| V <sub>OH</sub>    | HIGH Level Output Voltage                      | I <sub>OH</sub> = -4 mA                                                      | GPIO[3:0],<br>REG_GPIO[8:             | V <sub>DDIO</sub> -<br>0.45 |      | $V_{DDIO}$                  | V    |

| V <sub>OL</sub>    | LOW Level Output Voltage                       | I <sub>OL</sub> = +4 mA                                                      | 5], MCLK,<br>12S_WC,                  | 0                           |      | 0.45                        | V    |

| Ios                | Output Short Circuit Current                   | V <sub>OUT</sub> = 0 V <sup>(5)</sup>                                        | 12S_CLK,                              |                             | -35  |                             | mA   |

| l <sub>OZ</sub>    | TRI-STATE® Output Current                      | $V_{OUT} = 0 \text{ V or } V_{DDIO}, PDB = L,$                               | I2S_D[A:D],<br>LOCK, PASS             | -20                         |      | 20                          | μА   |

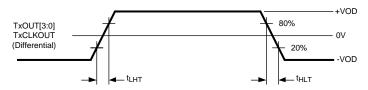

|                    | (OpenLDI) LVDS OUTPUT                          | 25.0                                                                         | LOOK, 1 AOO                           |                             |      |                             | •    |

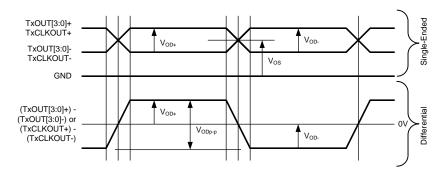

| V <sub>OD</sub>    | Output Voltage Swing (single-                  | Register $0x4B[1:0] = b'00$<br>R <sub>L</sub> = $100 \Omega$                 |                                       | 140                         | 200  | 300                         | mV   |

| - 00               | ended)                                         | Register 0x4B[1:0] = b'01<br>R <sub>L</sub> = 100 $\Omega$                   | TxCLK±,                               | 220                         | 300  | 380                         |      |

| V                  | Differential Output Voltage                    | Register $0x4B[1:0] = b'00$<br>R <sub>L</sub> = $100 \Omega$                 | TxOUT[3:0]±                           |                             | 400  |                             | mV   |

| V <sub>ODp-p</sub> | Differential Output Voltage                    | Register $0x4B[1:0] = b'01$<br>R <sub>L</sub> = $100 \Omega$                 |                                       |                             | 600  |                             |      |

| $\Delta V_{OD}$    | Output Voltage Unbalance                       | $R_L = 100 \Omega$                                                           |                                       |                             | 1    | 50                          | mV   |

| Vos                | Common Mode Voltage                            |                                                                              |                                       | 1.125                       | 1.25 | 1.375                       | ٧    |

| $\Delta V_{OS}$    | Offset Voltage Unbalance                       |                                                                              |                                       |                             | 1    | 50                          | mV   |

| I <sub>OS</sub>    | Output Short Circuit Current                   | V <sub>OUT</sub> = GND                                                       |                                       |                             | -5   |                             | mA   |

| I <sub>OZ</sub>    | Output TRI-STATE® Current                      | OEN = GND, $V_{OUT} = V_{DDIO}$ or GND, 0.8 $V \le V_{IN} \le 1.6 \text{ V}$ |                                       | -500                        |      | 500                         | μΑ   |

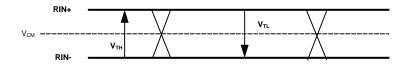

| FPD-LINK           | III RECEIVER                                   |                                                                              |                                       |                             |      | •                           |      |

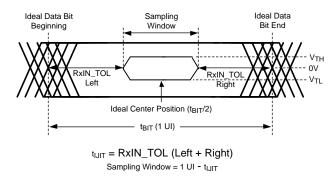

| $V_{TH}$           | Input Threshold High                           |                                                                              |                                       |                             |      | 50                          | mV   |

| V <sub>TL</sub>    | Input Threshold Low                            | V <sub>CM</sub> = 2.1 V (Internal V <sub>BIAS</sub> )                        |                                       | -50                         |      |                             | mV   |

| $V_{\text{ID}}$    | Input Differential Threshold                   |                                                                              | RIN±                                  |                             |      | 100                         | mV   |

| $V_{CM}$           | Common-mode Voltage                            |                                                                              |                                       |                             | 2.1  |                             | V    |

| $R_{T}$            | Internal Termination Resistance (Differential) |                                                                              |                                       | 80                          | 100  | 120                         | Ω    |

| SUPPLY (           | CURRENT                                        |                                                                              |                                       |                             |      |                             |      |

| I <sub>DD1</sub>   |                                                |                                                                              | V <sub>DD33</sub> = 3.6 V             |                             | 190  | 250                         | mA   |

| lanua :            |                                                | Checkerboard Pattern                                                         | $V_{DDIO} = 3.6 \text{ V}$            |                             | 0.1  | 1                           | mA   |

| I <sub>DDIO1</sub> | Supply Current                                 |                                                                              | V <sub>DDIO</sub> = 1.89 V            |                             | 0.1  | 1                           | mA   |

| I <sub>DD2</sub>   | $R_L = 100 \Omega$ ,<br>PCLK = 85 MHz          |                                                                              | V <sub>DD33</sub> = 3.6 V             |                             | 185  |                             | mA   |

| Innios             |                                                | Random Pattern                                                               | $V_{DDIO} = 3.6 \text{ V}$            |                             | 0.1  |                             | mA   |

| I <sub>DDIO2</sub> |                                                |                                                                              | $V_{\rm DDIO} = 1.89 \text{ V}$       |                             | 0.1  |                             | mA   |

| $I_{DDZ}$          |                                                | DDD = 0.1/ All athor 1.1/04/00                                               | $V_{DD33} = 3.6 \text{ V}$            |                             | 3    | 8                           | mA   |

| I <sub>DDIOZ</sub> | Supply Current — Power Down                    | PDB = 0 V, All other LVCMOS inputs = 0 V                                     | $V_{DDIO} = 3.6 \text{ V}$            |                             | 100  | 500                         | μΑ   |

| -טוטע              |                                                |                                                                              | $V_{DDIO} = 1.89 V$                   |                             | 50   | 250                         | μΑ   |

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

#### 7.6 AC Electrical Characteristics

Over recommended operating supply and temperature ranges unless otherwise specified. (1) (2) (3)

| PARAMETER            |                                                              | TEST CONDITIONS PIN/FREQ.                                            |                                            | MIN TYP          | MAX                                   | UNIT             |

|----------------------|--------------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------|------------------|---------------------------------------|------------------|

| GPIO                 |                                                              |                                                                      |                                            |                  |                                       |                  |

| t <sub>GPIO,FC</sub> | GPIO Pulse Width, Forward<br>Channel                         | See <sup>(4)</sup>                                                   | GPIO[3:0],<br>PCLK = 5<br>MHz to 85<br>MHz | 2/PCLK           |                                       | s                |

| $t_{\text{GPIO},BC}$ | GPIO Pulse Width, Back Channel                               | See (4)                                                              | GPIO[3:0]                                  | 20               |                                       | μs               |

| RESET                |                                                              |                                                                      |                                            |                  |                                       |                  |

| t <sub>LRST</sub>    | PDB Reset Low Pulse                                          | See (4)                                                              | PDB                                        | 2                |                                       | ms               |

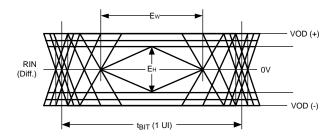

| LOOP-TH              | ROUGH MONITOR OUTPUT                                         |                                                                      |                                            |                  |                                       |                  |

| $E_W$                | Differential Output Eye Opening Width                        | $R_L = 100 \Omega$ , Jitter freq > f/40                              | CMLOUTP,<br>CMLPUTN                        | 0.4              |                                       | UI               |

| E <sub>H</sub>       | Differential Output Eye Height                               |                                                                      |                                            | 300              |                                       | mV               |

| FPD-LINK             | LVDS OUTPUT                                                  | 1                                                                    |                                            |                  | L                                     |                  |

| t <sub>TLHT</sub>    | Low to High Transition Time                                  | $R_L = 100 \Omega$                                                   | TxCLK±,                                    | 0.25             | 0.5                                   | ns               |

| t <sub>THLT</sub>    | High to Low Transition Time                                  | -                                                                    | TxOUT[3:0]±                                | 0.25             | 0.5                                   | ns               |

| t <sub>DCCJ</sub>    | Cycle-to-Cycle Output Jitter                                 | PCLK = 5 MHz                                                         | TxCLK±                                     | 170              | 275                                   | ps               |

| : = = =              |                                                              | PCLK = 85 MHz                                                        | 7                                          | 35               | 55                                    |                  |

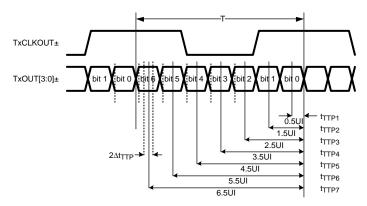

| t <sub>TTPn</sub>    | Transmitter Pulse Position                                   | 5 MHz ≤ PCLK ≤ 85 MHz<br>n = [6:0] for bits [6:0]<br>See Figure 13   | TxOUT[3:0]±                                | 0.5 + n          |                                       | UI               |

| $\Delta t_{TTP}$     | Offset Transmitter Pulse Position (bit 6 - bit 0)            | PCLK = 85 MHz                                                        |                                            | 0.1              |                                       | UI               |

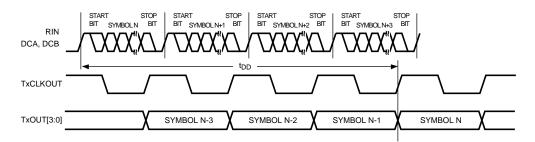

| t <sub>DD</sub>      | Delay Latency                                                |                                                                      |                                            | 147*T            |                                       | Т                |

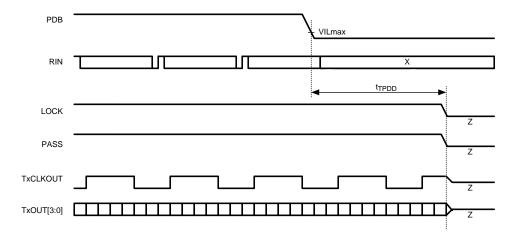

| t <sub>TPDD</sub>    | Power Down Delay Active to OFF                               |                                                                      |                                            | 900              |                                       | μs               |

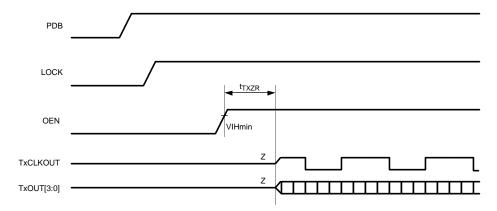

| t <sub>TXZR</sub>    | Enable Delay OFF to Active                                   |                                                                      |                                            | 6                |                                       | ns               |

|                      | ( III INPUT                                                  | 1                                                                    |                                            |                  |                                       |                  |

| IJT                  | Input Jitter <sup>(5)</sup>                                  | PCLK = 5 MHz to 85 MHz<br>Sinusoidal Jitter Frequency ><br>PCLK / 15 | RIN±                                       |                  | 0.35                                  | UI               |

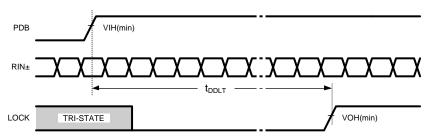

| t <sub>DDLT</sub>    | Lock Time <sup>(4)</sup>                                     | 5 MHz ≤ PCLK ≤ 85 MHz                                                | RIN±, LOCK                                 | 6                | 40                                    | ms               |

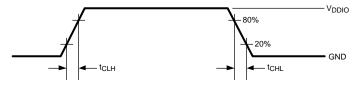

|                      | OUTPUTS                                                      | •                                                                    |                                            |                  | · · · · · · · · · · · · · · · · · · · |                  |

| t <sub>CLH</sub>     | Low-to-High Transition Time                                  | C <sub>L</sub> = 8 pF                                                | LOCK, PASS                                 | 3                | 7                                     | ns               |

| t <sub>CHL</sub>     | High-to-Low Transition Time                                  | 1                                                                    |                                            | 2                | 5                                     | ns               |

| BIST MOI             | DE                                                           | 1                                                                    |                                            |                  | L                                     |                  |

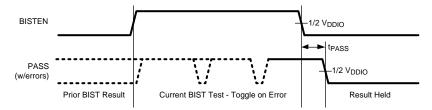

| t <sub>PASS</sub>    | BIST PASS Valid Time                                         |                                                                      | PASS                                       | 800              |                                       | ns               |

|                      | ISMITTER                                                     | 1                                                                    |                                            |                  |                                       |                  |

| tJ                   | Clock Output Jitter                                          |                                                                      | MCLK                                       | 2                |                                       | ns               |

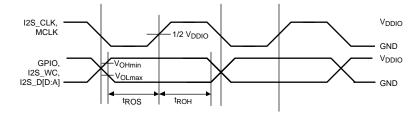

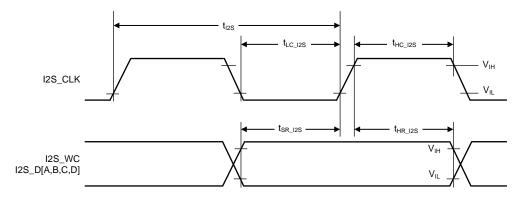

| T <sub>I2S</sub>     | I2S Clock Period<br>Figure 10, <sup>(4)</sup> <sup>(6)</sup> | PCLK=5 MHz to 85 MHz                                                 | I2S_CLK,<br>PCLK = 5<br>MHz to 85<br>MHz   | 2/PCLK<br>or >77 |                                       | ns               |

| T <sub>HC</sub>      | I2S Clock High Time<br>Figure 10, <sup>(6)</sup>             |                                                                      | I2S_CLK                                    | 0.35             |                                       | T <sub>I2S</sub> |

<sup>(1)</sup> The Electrical Characteristics tables list ensured specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics conditions and/or notes. Typical specifications are estimations only and are not ensured.

Copyright © 2013–2016, Texas Instruments Incorporated

<sup>(2)</sup> Typical values represent most likely parametric norms at V<sub>DD33</sub> = 3.3 V, V<sub>DDIO</sub> = 1.8 V or 3.3 V, T<sub>A</sub> = 25°C, and at the *Recommended Operating Conditions* at the time of product characterization and are not ensured.

<sup>(3)</sup> Current into device pins is defined as positive. Current out of a device pin is defined as negative. Voltages are referenced to ground except V<sub>OD</sub> and ΔV<sub>OD</sub>, which are differential voltages.

<sup>(4)</sup> Specification is ensured by design and is not tested in production.

<sup>(5)</sup> UI – Unit Interval is equivalent to one serialized data bit width 1UI = 1 / (35 x PCLK). The UI scales with PCLK frequency.

<sup>(6)</sup> I2S specifications for t<sub>LC</sub> and t<sub>HC</sub> pulses must each be greater than 1 PCLK period to ensure sampling and supersedes the 0.35\*T<sub>I2S\_CLK</sub> requirement. t<sub>LC</sub> and t<sub>HC</sub> must be longer than the greater of either 0.35\*T<sub>I2S\_CLK</sub> or 2\*PCLK.

## **AC Electrical Characteristics (continued)**

Over recommended operating supply and temperature ranges unless otherwise specified. (1) (2) (3)

|                     | PARAMETER                                       | TEST CONDITIONS | PIN/FREQ.            | MIN  | TYP MAX | UNIT             |

|---------------------|-------------------------------------------------|-----------------|----------------------|------|---------|------------------|

| T <sub>LC</sub>     | I2S Clock Low Time<br>Figure 10, <sup>(6)</sup> |                 | I2S_CLK              | 0.35 |         | T <sub>I2S</sub> |

| t <sub>SR_I2S</sub> | I2S Set-up Time<br>Figure 10, <sup>(6)</sup>    |                 | I2S_WC<br>I2S_D[A:D] | 0.2  |         | T <sub>I2S</sub> |

| t <sub>HR_I2S</sub> | I2S Hold Time<br>Figure 10, <sup>(6)</sup>      |                 | I2S_WC<br>I2S_D[A:D] | 0.2  |         | T <sub>I2S</sub> |

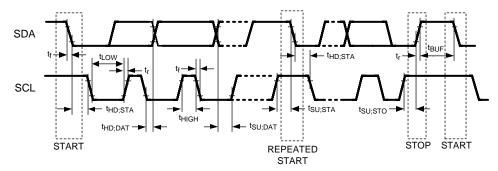

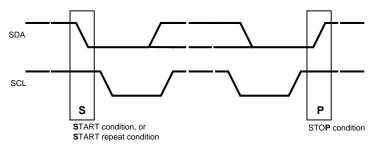

## 7.7 Timing Requirements for the Serial Control Bus

Over 3.3-V supply and temperature ranges unless otherwise specified. (1) (2)

|                     |                                                       |               | MIN | TYP MAX | UNIT |

|---------------------|-------------------------------------------------------|---------------|-----|---------|------|

| f <sub>SCL</sub>    | CCI Clask Francisco                                   | Standard Mode | 0   | 100     | kHz  |

|                     | SCL Clock Frequency                                   | Fast Mode     | 0   | 400     | kHz  |

| $t_{LOW}$           | CCL Law Davied                                        | Standard Mode | 4.7 |         | μs   |

|                     | SCL Low Period                                        | Fast Mode     | 1.3 |         | μs   |

| t <sub>HIGH</sub>   | CCL High David                                        | Standard Mode | 4.0 |         | μs   |

|                     | SCL High Period                                       | Fast Mode     | 0.6 |         | μs   |

| t <sub>HD;STA</sub> | Hold time for a start or a                            | Standard Mode | 4.0 |         | μs   |

|                     | repeated start condition                              | Fast Mode     | 0.6 |         | μs   |

| t <sub>SU:STA</sub> | Set Up time for a start or a repeated start condition | Standard Mode | 4.7 |         | μs   |

|                     |                                                       | Fast Mode     | 0.6 |         | μs   |

| t <sub>HD;DAT</sub> | Data Hold Time                                        | Standard Mode | 0   | 3.45    | μs   |

|                     |                                                       | Fast Mode     | 0   | 0.9     | μs   |

| t <sub>SU:DAT</sub> | Data Set Up Time                                      | Standard Mode | 250 |         | ns   |

|                     |                                                       | Fast Mode     | 100 |         | ns   |

| t <sub>SU;STO</sub> | Set Up Time for STOP                                  | Standard Mode | 4   |         | μs   |

|                     | Condition (3)                                         | Fast Mode     | 0.6 |         | μs   |

|                     | Bus Free Time                                         | Standard Mode | 4.7 |         | μs   |

| t <sub>BUF</sub>    | Between STOP and START                                | Fast Mode     | 1.3 |         | μs   |

|                     | SCL & SDA Rise Time,                                  | Standard Mode |     | 1000    | ns   |

| t <sub>r</sub>      | (3)                                                   | Fast Mode     |     | 300     | ns   |

|                     | SCL & SDA Fall Time,                                  | Standard Mode |     | 300     | ns   |

| t <sub>f</sub>      | (3)                                                   | Fast mode     |     | 300     | ns   |

<sup>(1)</sup> The Electrical Characteristics tables list ensured specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics conditions and/or notes. Typical specifications are estimations only and are not ensured.

## 7.8 Timing Requirements

|                     | 9                    |                        |     |     |     |      |

|---------------------|----------------------|------------------------|-----|-----|-----|------|

|                     |                      |                        | MIN | NOM | MAX | UNIT |

| $t_R$               | SDA RiseTime – READ  | SDA, RPU = 10 kΩ, Cb ≤ |     | 430 |     | ns   |

| $t_{F}$             | SDA Fall Time – READ | 400 pF, Figure 16      |     | 20  |     | ns   |

| t <sub>SU;DAT</sub> | Set Up Time – READ   | Figure 16              |     | 560 |     | ns   |

| t <sub>HD;DAT</sub> | Hold Up Time – READ  | Figure 16              |     | 615 |     | ns   |

<sup>(2)</sup> Typical values represent most likely parametric norms at V<sub>DD33</sub> = 3.3 V, V<sub>DDIO</sub> = 1.8 V or 3.3 V, T<sub>A</sub> = +25°C, and at the *Recommended Operating Conditions* at the time of product characterization and are not ensured.

<sup>(3)</sup> Specification is ensured by design and is not tested in production.

## 7.9 DC and AC Serial Control Bus Characteristics

Over 3.3 V supply and temperature ranges unless otherwise specified. (1) (2) (3)

|                 | PARAMETER               | TEST CONDITIONS                        | MIN                       | TYP MA                | X UNIT |

|-----------------|-------------------------|----------------------------------------|---------------------------|-----------------------|--------|

| $V_{IH}$        | Input High Level        | SDA and SCL                            | 0.7*<br>V <sub>DDIO</sub> | V <sub>DD</sub>       | 33 V   |

| $V_{IL}$        | Input Low Level Voltage | SDA and SCL                            | GND                       | 0.<br>V <sub>DD</sub> | \ \/   |

| $V_{HY}$        | Input Hysteresis        |                                        |                           | 50                    | mV     |

| $V_{OL}$        |                         | SDA or SCL, I <sub>OL</sub> = 1.25 mA  | 0                         | 0.3                   | 36 V   |

| I <sub>in</sub> |                         | SDA or SCL, $V_{IN} = V_{DDIO}$ or GND | -10                       |                       | 0 μΑ   |

| t <sub>SP</sub> | Input Filter            |                                        |                           | 50                    | ns     |

| C <sub>in</sub> | Input Capacitance       | SDA or SCL                             |                           | 5                     | pF     |

- (1) The Electrical Characteristics tables list specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics conditions and/or notes. Typical specifications are estimations only and are not ensured.

- (2) Typical values represent most likely parametric norms at V<sub>DD33</sub> = 3.3 V, V<sub>DDIO</sub> = 1.8 V or 3.3 V, T<sub>A</sub> = +25°C, and at the *Recommended Operating Conditions* at the time of product characterization and are not ensured.

- (3) Current into device pins is defined as positive. Current out of a device pin is defined as negative. Voltages are referenced to ground except V<sub>OD</sub> and ΔV<sub>OD</sub>, which are differential voltages.

Figure 1. Checkerboard Data Pattern

Figure 2. CML Output Driver

Figure 3. LVCMOS Transition Times

Figure 4. Latency Delay

Figure 5. FPD-Link & LVCMOS Power Down Delay

Figure 6. FPD-Link Outputs Enable Delay

Figure 7. CML PLL Lock Time

Figure 8. FPD-Link III Receiver DC  $V_{TH}/V_{TL}$  Definition

Figure 9. Output Data Valid (Setup and Hold) Times

Figure 10. Output State (Setup and Hold) Times

**Figure 11. Input Transition Times**

Figure 12. FPD-Link Single-Ended and Differential Waveforms

Figure 13. FPD-Link Transmitter Pulse Positions

Figure 14. Receiver Input Jitter Tolerance

Figure 15. BIST PASS Waveform

Figure 16. Serial Control Bus Timing Diagram

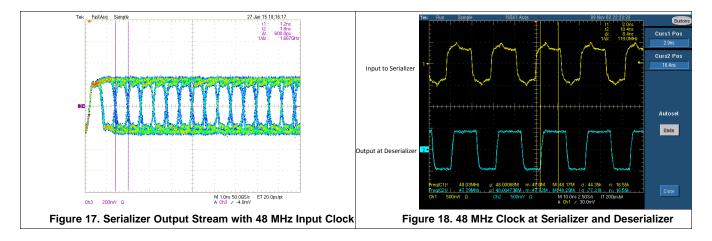

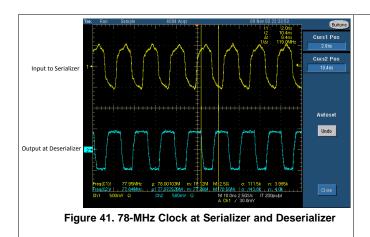

# 7.10 Typical Characteristics

## 8 Detailed Description

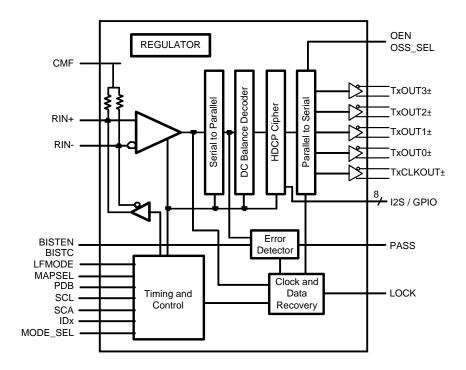

#### 8.1 Overview

The DS90UH928Q-Q1 receives a 35-bit symbol over a single serial FPD-Link III pair operating at up to 2.975 Gbps line rate and converts this stream into an FPD-Link Interface (4 LVDS data channels + 1 LVDS Clock). The FPD-Link III serial stream contains an embedded clock, video control signals, and the DC-balanced video data and audio data which enhance signal quality to support AC coupling.

The DS90UH928Q-Q1 deserializer attains lock to a data stream without the use of a separate reference clock source, which greatly simplifies system complexity and overall cost. The deserializer also synchronizes to the serializer regardless of the data pattern, delivering true automatic *plug and lock* performance. It can lock to the incoming serial stream without the need of special training patterns or sync characters. The deserializer recovers the clock and data by extracting the embedded clock information, validating then deserializing the incoming data stream. It also applies decryption through a High-Bandwidth Digital Content Protection (HDCP) Cipher to this video and audio data stream following reception of the data from the FPD-Link III decoder. On-chip non-volatile memory stores the HDCP keys. All key exchange is done through the FPD-Link III bidirectional control interface. The decrypted FPD-Link LVDS video bus is provided to the display.

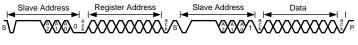

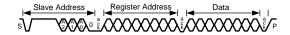

The DS90UH928Q-Q1 deserializer incorporates an I<sup>2</sup>C-compatible interface. The I<sup>2</sup>C-compatible interface allows programming of serializer or deserializer devices from a local host controller. In addition, the serializer/deserializer devices incorporate a bidirectional control channel (BCC) that allows communication between serializer/deserializer as well as remote I2C slave devices.

The bidirectional control channel (BCC) is implemented via embedded signaling in the high-speed forward channel (serializer to deserializer) combined with lower speed signaling in the reverse channel (deserializer to serializer). Through this interface, the BCC provides a mechanism to bridge I<sup>2</sup>C transactions across the serial link from one I<sup>2</sup>C bus to another. The implementation allows for arbitration with other I<sup>2</sup>C compatible masters at either side of the serial link.

The DS90UH928Q-Q1 deserializer is intended for use with DS90UH925Q-Q1 or DS90UH927Q-Q1 serializers, but is also backward compatible with DS90UR905Q and DS90UR907Q FPD-Link II serializers.

## 8.2 Functional Block Diagram

Submit Documentation Feedback

Copyright © 2013–2016, Texas Instruments Incorporated

### 8.3 Feature Description

### 8.3.1 High Speed Forward Channel Data Transfer

The High-Speed Forward Channel is composed of a 35-bit frame containing video data, sync signals, HDCP, I<sup>2</sup>C, and I2S audio transmitted from serializer to deserializer. Figure 19 illustrates the serial stream PCLK cycle. This data payload is optimized for signal transmission over an AC-coupled link. Data is randomized, DC-balanced and scrambled.

Figure 19. FPD-Link III Serial Stream

The device supports pixel clock ranges of 5 MHz to 15 MHz (LFMODE=1) and 15 MHz to 85 MHz (LFMODE=0). This corresponds to an application payload rate range of 175 Mbps to 2.975 Gbps, with an actual line rate range of 525 Mbps to 2.975 Gbps.

### 8.3.2 Low-Speed Back Channel Data Transfer

The Low-Speed Back Channel of the DS90UH928Q-Q1 provides bidirectional communication between the display and host processor. The back channel control data is transferred over the single serial link along with the high-speed forward data, DC balance coding and embedded clock information. Together, the forward channel and back channel for the bidirectional control channel (BCC). This architecture provides a backward path across the serial link together with a high speed forward channel. The back channel contains the I<sup>2</sup>C, HDCP, CRC and 4 bits of standard GPIO information with 10 Mbps line rate.

### 8.3.3 Backward Compatible Mode

The DS90UH928Q-Q1 is also backward compatible to the DS90UR905Q and DS90UR907Q FPD-Link II serializes with 15 MHz to 65 MHz PCLK frequencies supported. It receives 28-bits of data over a single serial FPD-Link II pair operating at a payload rate of 420 Mbps to 1.82 Gbps. This backward compatibility configuration is provided through the MODE\_SEL pin or programmed through the device control registers (Table 8). The bidirectional control channel, HDCP, bidirectional GPIOs, I2S, and interrupt (INTB) are not active in this mode. However, local I<sup>2</sup>C access to the serializer is still available.

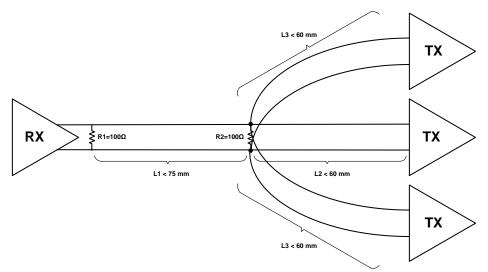

#### 8.3.4 Input Equalization

An FPD-Link III input adaptive equalizer provides compensation for transmission medium losses and reduces medium-induced deterministic jitter. It supports STP cables up to 10 meters total cable length with 3 inline connectors at maximum serializer stream payload rate of 2.975 Gbps.

The adaptive equalizer may be set to a Long Cable Mode (LCBL), using the MODE\_SEL pin (Table 6). This mode is typically used with longer cables where it may be desirable to start adaptive equalization from a higher default gain. In this mode, the device attempts to lock from a minimum floor AEQ value, defined by a value stored in the control registers (Table 8).

## 8.3.5 Common Mode Filter Pin (CMF)

The deserializer provides access to the center tap of the internal CML termination. A 0.1  $\mu$ F capacitor must be connected from this pin to GND for additional common-mode filtering of the differential pair (Figure 39). This increases noise rejection capability in high-noise environments.

#### 8.3.6 Power Down (PDB)

The deserializer has a PDB input pin to enable or power down the device. This pin may be controlled by an external device, or through  $V_{DDIO}$ , where  $V_{DDIO}=3$  V to 3.6 V or  $V_{DD33}$ . To save power, disable the link when the display is not needed (PDB = LOW). Ensure that this pin is not driven HIGH before  $V_{DD33}$  and  $V_{DDIO}$  have reached final levels. When PDB is driven low, ensure that the pin is driven to 0 V for at least 1.5 ms before releasing or driving high (See ). If the PDB is pulled up to  $V_{DDIO}=3$  V to 3.6 V or  $V_{DD33}$  directly, a 10 k $\Omega$  pullup resistor and a >10  $\mu$ F capacitor to ground are required (see Figure 39).

Toggling PDB low will POWER DOWN the device and RESET all control registers to default. During this time, PDB must be held low for a minimum of 2 ms (see ).

Copyright © 2013–2016, Texas Instruments Incorporated

### 8.3.7 Video Control Signals

The video control signal bits embedded in the high-speed FPD-Link LVDS are subject to certain limitations relative to the video pixel clock period (PCLK). By default, the device applies a minimum pulse width filter on these signals to help eliminate spurious transitions.

Normal Mode Control Signals (VS, HS, DE) have the following restrictions:

- Horizontal Sync (HS): The video control signal pulse width must be 3 PCLKs or longer when the Control Signal Filter (register bit 0x03[4]) is enabled (default). Disabling the Control Signal Filter removes this restriction (minimum is 1 PCLK). See Table 8. HS can have at most two transitions per 130 PCLKs.

- Vertical Sync (VS): The video control signal pulse is limited to 1 transition per 130 PCLKs. Thus, the minimum pulse width is 130 PCLKs.

- Data Enable Input (DE): The video control signal pulse width must be 3 PCLKs or longer when the Control Signal Filter (register bit 0x03[4]) is enabled (default). Disabling the Control Signal Filter removes this restriction (minimum is 1 PCLK). See Table 8. DE can have at most two transitions per 130 PCLKs.

#### 8.3.8 EMI Reduction Features

## 8.3.8.1 LVCMOS VDDIO Option

The 1.8 V/3.3 V LVCMOS inputs and outputs are powered from a separate VDDIO supply pin to offer compatibility with external system interface signals. Note: When configuring the  $V_{DDIO}$  power supplies, all the single-ended control input pins (except PDB) for device need to scale together with the same operating  $V_{DDIO}$  levels. If  $V_{DDIO}$  is selected to operate in the 3.0 V to 3.6 V range,  $V_{DDIO}$  must be operated within 300 mV of  $V_{DD33}$  (See *Recommended Operating Conditions*).

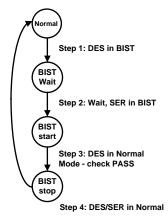

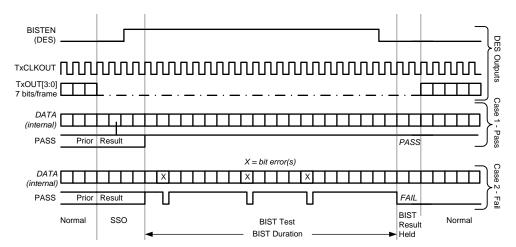

### 8.3.9 Built In Self Test (BIST)

An optional At-Speed Built-In Self Test (BIST) feature supports testing of the high-speed serial link and the low-speed back channel without external data connections. This is useful in the prototype stage, equipment production, in-system test, and system diagnostics.

## 8.3.9.1 BIST Configuration and Status

The BIST mode is enabled at the descrializer by pin (BISTEN) or BIST configuration register. The test may select either an external PCLK or the 33 MHz internal oscillator clock (OSC) frequency. In the absence of PCLK, the user can select the internal OSC frequency at the descrializer through the BISTC pin or BIST configuration register.