DS90UR910-Q1

SNLS414E -JUNE 2012-REVISED OCTOBER 2016

# DS90UR910-Q1 10 to 75 MHz 24-bit Color FPD-Link II to CSI-2 Converter

## **Features**

- Automotive Grade Product: AEC-Q100 Grade 2 Qualified

- 10- to 75-MHz PCLK Support (280-Mbps to 2.1-Gbps FPD-Link II Linerate)

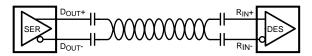

- Compatible to DC Balanced, AC-Coupled for FPD-Link II Serial Bit Stream

- Capable to Recover Data up to 10 Meters STP Cable

- MIPI D-PHY Modules Conform to v1.00.00

- Compatible With MIPI CSI-2 Version 1.01

- Supports Data Rate up to 900 Mbps per Data Lane With Two Lanes

- Video Stream Packet Formats: RGB888

- Continuous and Non-Continuous Clocking Mode

- Ultra Low Power, Escape, High Speed, and Control Modes Support

- Integrated Input Terminations and Adjustable Receive Equalization

- Fast Random Lock (No Reference Clock Required)

- CCI (Camera Control Interface) and I2C Compatible Control Bus

- @Speed BIST and Reporting Pin

- Single 1.8-V Power Supply

- 1.8-V or 3.3-V Compatible LVCMOS I/O Interface

- 8-kV ISO 10605 ESD Rating

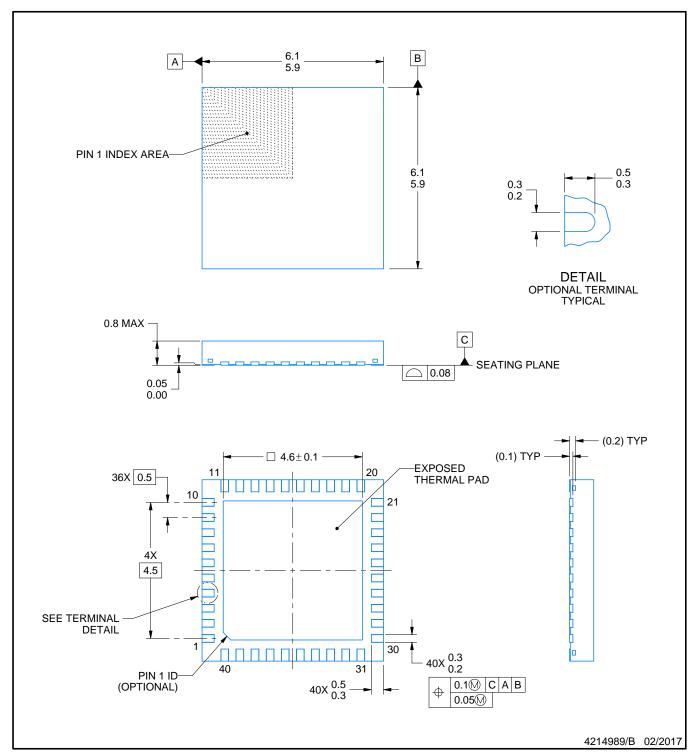

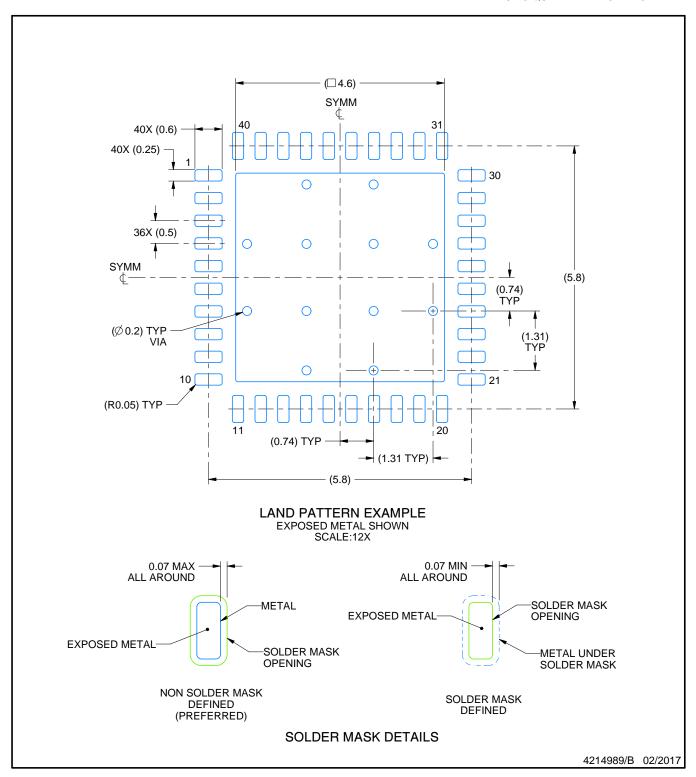

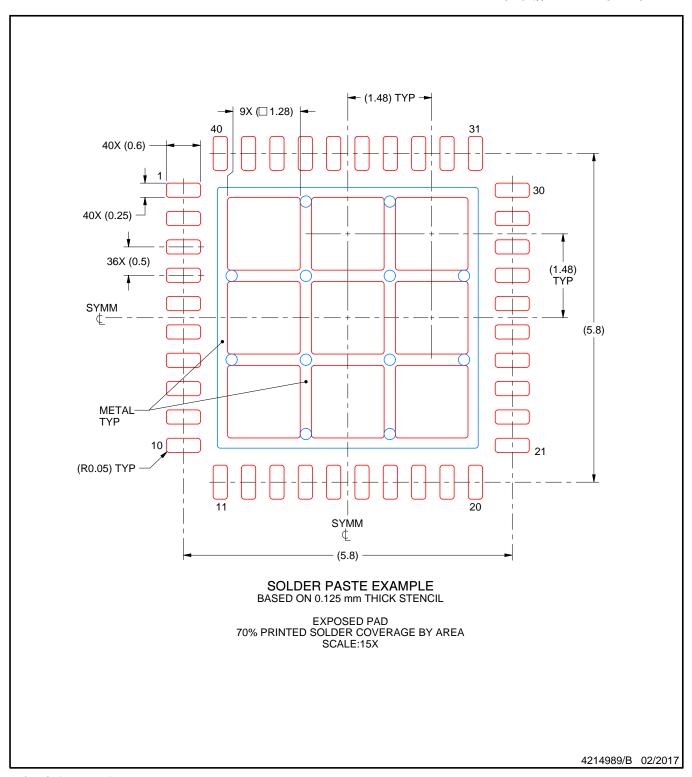

- Leadless 40-Pin WQFN Package (6 mm × 6 mm)

# 2 Applications

- Automotive Infotainment:

- Central Information Displays

- Rear Seat Entertainment Systems

- **Digital Instrument Clusters**

# 3 Description

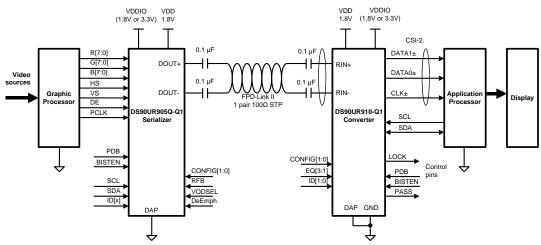

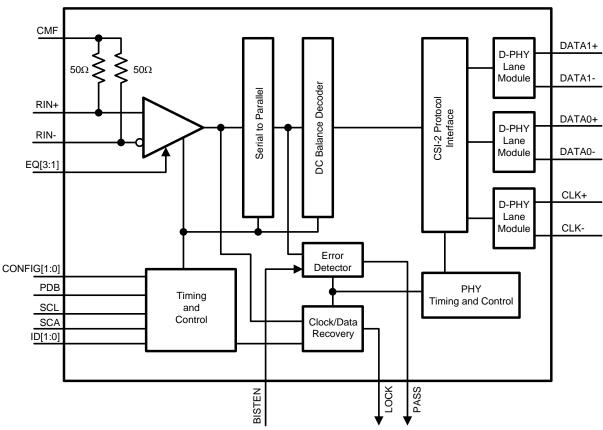

The DS90UR910-Q1 is an interface bridge chip that recovers data from the FPD-Link II serial bit stream and converts into a Camera Serial Interface (CSI-2) format compatible with Mobile Industry Processor Interface (MIPI) specifications. It recovers the 24- or 18-bit RGB data and 3 video sync-signals from the serial bit stream compatible to FPD-Link II serializers. The recovered data is packetized and serialized over two data lanes strobed by a half-rate serial clock compliant with the MIPI DPHY and CSI-2 specifications, each running up to 900 Mbps. The FPD-Link II receiver supports pixel clocks of up to 75 MHz. The CSI-2 output serial bus greatly reduces the interconnect and signal count to a graphic processing unit (GPU) and eases system designs for video streams from multiple automotive driver assist cameras.

The DS90UR910-Q1 is available in a 40-pin WQFN package. Electrical performance is qualified for automotive AEC-Q100 grade 2 temperature range -40°C to 105°C.

## Device Information (1)

| PART NUMBER  | PACKAGE   | BODY SIZE         |  |

|--------------|-----------|-------------------|--|

| DS90UR910-Q1 | WQFN (40) | 6.00 mm x 6.00 mm |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

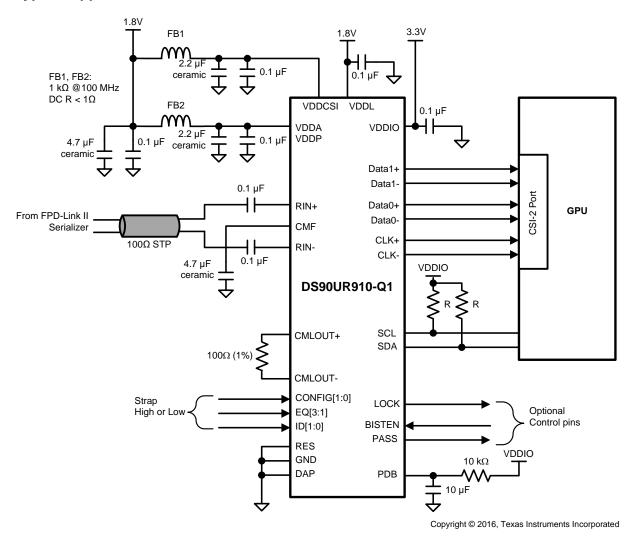

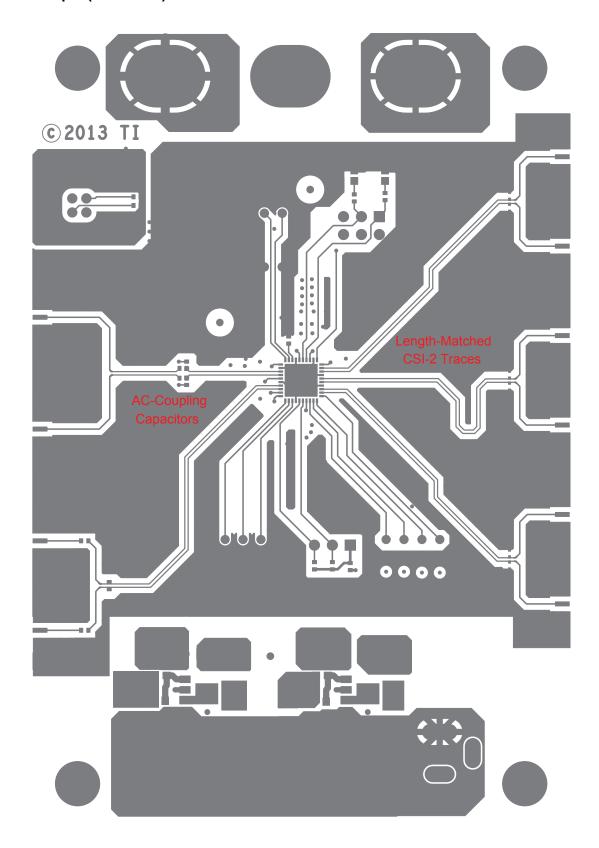

#### **Applications Diagram**

Copyright © 2016. Texas Instruments Incorporated

# **Table of Contents**

| 1 Features       1       7.3 Feature Description         2 Applications       1       7.4 Device Functional Modes | 19                |

|-------------------------------------------------------------------------------------------------------------------|-------------------|

| Z Applications                                                                                                    |                   |

| 3 Description                                                                                                     | 2                 |

| 4 Revision History                                                                                                | 2                 |

| 5 Pin Configuration and Functions                                                                                 | 2                 |

| 6 Specifications 5 8.2 Typical Application                                                                        | 2                 |

| 6.1 Absolute Maximum Ratings                                                                                      | <u>2</u>          |

| 6.2 ESD Ratings                                                                                                   | Pin 2             |

| 6.3 Recommended Operating Conditions                                                                              | 2 <sup>-</sup>    |

| 6.4 Thermal Information                                                                                           | 2                 |

| 6.5 Electrical Characteristics: DC                                                                                | 2                 |

| 6.6 Switching Characteristics: AC                                                                                 | ort 30            |

| 6.7 Timing Requirements: Serial Control Bus (CCI and 11.1 Documentation Support                                   | 3                 |

| I2C)                                                                                                              | ntation Updates 3 |

| 6.8 Timing Requirements: DC and AC Serial Control Bus 11.3 Community Resources                                    | 3                 |

| (CCI and I2C)                                                                                                     | 3                 |

| 6.9 Typical Characteristics                                                                                       | 3                 |

| 7 Detailed Description                                                                                            | 3                 |

| 7.1 Overview 14 12 Mechanical, Packaging, and Orde                                                                | rable             |

| 7.2 Functional Block Diagram                                                                                      |                   |

|                                                                                                                   |                   |

# 4 Revision History

| Changes from Revision D (July 2015) to Revision E                  | Page |

|--------------------------------------------------------------------|------|

| Added Device Functional Modes and Application Information sections | 1    |

| Added Thermal Information table                                    | 6    |

| Changes from Revision C (May 2013) to Revision D                   | Page |

| Changed device status from Product Preview to Production Data      |      |

| Added new section titles to update to new TI format                | 1    |

| Changes from Revision B (October 2012) to Revision C               | Page |

| Changed layout of National Semiconductor Data Sheet to TI format   | 1    |

| Changed Pin # for VDDL and VDDA Power pins for clarification       | 4    |

| Changes from Revision A (September 2012) to Revision B             | Page |

| Changed Pin Diagram                                                | 3    |

| Changes from Original (June 2012) to Revision A                    | Page |

| DS90UR910-Q1 DATASHEET – Initial Release                           | 1    |

Submit Documentation Feedback

Copyright © 2012–2016, Texas Instruments Incorporated

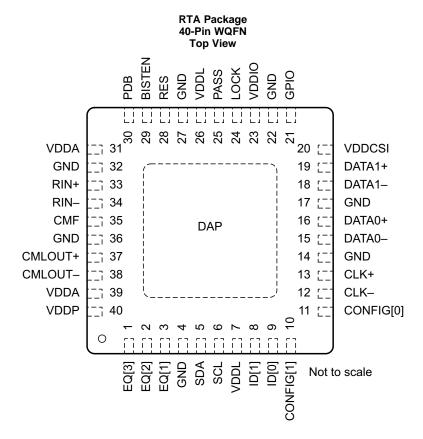

# 5 Pin Configuration and Functions

#### **Pin Functions**

| PII                 | PIN TYPE <sup>(1</sup> |      | DECORPORTION                                                                                                                                                                                                                                                               |  |  |  |

|---------------------|------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME <sup>(2)</sup> | NO.                    | ITPE | DESCRIPTION                                                                                                                                                                                                                                                                |  |  |  |

| FPD-LINK II SE      | RIAL INTER             | FACE |                                                                                                                                                                                                                                                                            |  |  |  |

| RIN+                | 33                     | 1    | CML, inverting and noninverting differential inputs. The inputs must be AC-coupled with a 100-nF capacitor.                                                                                                                                                                |  |  |  |

| RIN-                | 34                     | 1    | CML, inverting and noninverting differential inputs. The inputs must be AC-coupled with a 100-nF capacitor.                                                                                                                                                                |  |  |  |

| CMF                 | 35                     | ı    | Analog, common mode filter pin for the differential inputs. CMP is the virtual ground of the differential input stage. A bypass capacitor is connected from CMP to ground to increase the receiver's common mode noise immunity. TI recommends a 4.7-µF ceramic capacitor. |  |  |  |

| CMLOUT+             | 37                     | 0    | ML, inverting and noninverting differential outputs. Single $100-\Omega$ (1%) termination resistor muse placed across the CMLOUT± pins. Optional loop-through output to monitor post equalizer an equires use of the Serial Control Bus to enable.                         |  |  |  |

| CMLOUT-             | 38                     | 0    | CML, inverting and noninverting differential outputs. Single $100-\Omega$ (1%) termination resistor must be placed across the CMLOUT± pins. Optional loop-through output to monitor post equalizer and requires use of the Serial Control Bus to enable.                   |  |  |  |

| MIPI INTERFAC       | CE                     |      |                                                                                                                                                                                                                                                                            |  |  |  |

| DATA1+              | 19                     | 0    | DPHY, inverting and noninverting data output of DPHY Lane 1.                                                                                                                                                                                                               |  |  |  |

| DATA1-              | 18                     | 0    | DPHY, inverting and noninverting data output of DPHY Lane 1.                                                                                                                                                                                                               |  |  |  |

| DATA0+              | 16                     | 0    | DPHY, inverting and noninverting data output of DPHY Lane 0.                                                                                                                                                                                                               |  |  |  |

| DATA0-              | 15                     | 0    | DPHY, inverting and noninverting data output of DPHY Lane 0.                                                                                                                                                                                                               |  |  |  |

| CLK+                | 13                     | 0    | DPHY, inverting and noninverting half-rate DPHY clock lane.                                                                                                                                                                                                                |  |  |  |

| CLK-                | 12                     | 0    | DPHY, inverting and noninverting half-rate DPHY clock lane.                                                                                                                                                                                                                |  |  |  |

<sup>(1)</sup> G = Ground, I = Input, O = Output, P = Power

<sup>(2)</sup> 1 = HIGH, 0 = LOW

# Pin Functions (continued)

| PII                 | N                               |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------|---------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME <sup>(2)</sup> | NO.                             | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CONTROL ANI         | _                               | ATION               |                                                                                                                                                                                                                                                                                                                                                                                                                                    |

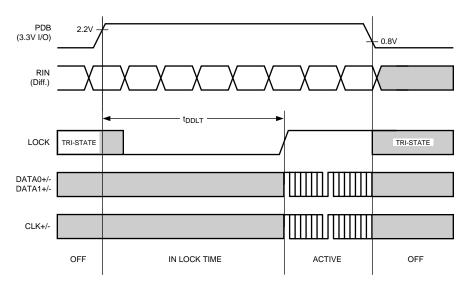

| PDB                 | 30                              | I                   | LVCMOS with pulldown, power down mode input; PDB = 1, Device is enabled (normal operation), PDB = 0, Device is in power-down, When the device is in the power-down, outputs are TRI-STATE, control registers are RESET.                                                                                                                                                                                                            |

| CONFIG[1:0]         | 10, 11                          | I                   | LVCMOS with pulldown, operating mode select; CONFIG[1:0] selects compatibility to FPD-Link II serializers. See Table 1.                                                                                                                                                                                                                                                                                                            |

| EQ[3:1]             | 1, 2, 3                         | I                   | LVCMOS with pulldown, receive equalization control; EQ[3:1] provides 8 combinations of the receive equalization gain settings. See Table 2. EQ[3:1] optimizes the input equalizer's ability to reduce inter-symbol interference from the loss characteristics of different cable lengths.                                                                                                                                          |

| BISTEN              | 29                              | 1                   | LVCMOS with pulldown, BIST enable input; BISTEN = 1, BIST is enabled, BISTEN = 0, BIST is disabled.                                                                                                                                                                                                                                                                                                                                |

| LOCK                | 24                              | 0                   | LVCMOS, LOCK status output; LOCK = 1, PLL acquired lock to the reference clock input; DPHY outputs are active LOCK = 0, PLL is unlocked                                                                                                                                                                                                                                                                                            |

| PASS                | 25                              | 0                   | LVCMOS, normal mode status output pin (BISTEN = 0); PASS = 1: No fault detected on input display timing, PASS = 0: Indicates an error condition or corruption in display timing. Fault condition occurs if: 1) DE length value mismatch measured once in succession, 2) VSync length value mismatch measured twice in succession, BIST mode status output pin (BISTEN = 1); PASS = 1: No error detected, PASS = 0: Error detected. |

| CCI AND I2C S       | ERIAL CONTI                     | ROL BUS             |                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SCL                 | 6                               | I                   | LVCMOS open drain, serial control bus clock input, SCL requires an external pullup resistor to V <sub>DDIO</sub> .                                                                                                                                                                                                                                                                                                                 |

| SDA                 | 5                               | I/O                 | LVCMOS open drain, serial control bus data input and output, SDA requires an external pullup resistor to V <sub>DDIO</sub> .                                                                                                                                                                                                                                                                                                       |

| ID[1:0]             | 8, 9                            | I                   | LVCMOS with pulldown, serial control bus device ID address select, see Table 6.                                                                                                                                                                                                                                                                                                                                                    |

| RESERVED PI         | NS                              |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| GPIO                | 21                              | I/O                 | General purpose I/O; Pin must be left floating during initial power-up.                                                                                                                                                                                                                                                                                                                                                            |

| RES                 | 28                              | I                   | LVCMOS with pulldown, reserved pin (must tie low)                                                                                                                                                                                                                                                                                                                                                                                  |

| POWER AND           | GROUND                          |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| VDDL                | 7, 26                           | Р                   | Power to logic circuitry, 1.8 V ±5%                                                                                                                                                                                                                                                                                                                                                                                                |

| VDDA                | 31, 39                          | Р                   | Power to analog circuitry, 1.8 V ±5%                                                                                                                                                                                                                                                                                                                                                                                               |

| VDDP                | 40                              | Р                   | Power to PLL, 1.8 V ±5%                                                                                                                                                                                                                                                                                                                                                                                                            |

| VDDCSI              | 20                              | Р                   | Power to DPHY CSI-2 drivers, 1.8 V ±5%                                                                                                                                                                                                                                                                                                                                                                                             |

| VDDIO               | 23                              | Р                   | Power to LVCMOS I/O circuitry, 1.8 V ±5% or 3.3 V ±10% (V <sub>DDIO</sub> )                                                                                                                                                                                                                                                                                                                                                        |

| GND                 | 4, 14, 17,<br>22, 27, 32,<br>36 | G                   | Ground return                                                                                                                                                                                                                                                                                                                                                                                                                      |

| GND                 | DAP                             | G                   | DAP is the metal contact at the bottom side, located at the center of the WQFN package. It must be connected to the GND plane with multiple via to lower the ground impedance and improve the thermal performance of the package. Connected to the ground plane (GND) with at least 9 vias.                                                                                                                                        |

Submit Documentation Feedback

Copyright © 2012–2016, Texas Instruments Incorporated

# 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)(2)

|                                                                                                                  |                                                                                     | MIN  | MAX               | UNIT  |

|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------|-------------------|-------|

| LVCMOS I/O voltage Receiver input voltage CSI-2 output voltage 40L WQFN package, maximi Junction temperature, TJ | V <sub>DDA</sub> , V <sub>DDP</sub> , V <sub>DDL</sub> , V <sub>DDCSI</sub> (1.8 V) | -0.3 | 2.5               |       |

| Supply voltage                                                                                                   | V <sub>DDIO</sub> (1.8-V I/O)                                                       | -0.3 | 2.5               | V     |

|                                                                                                                  | V <sub>DDIO</sub> (3.3-V I/O)                                                       | -0.3 | 4                 |       |

| LVCMOS I/O voltage                                                                                               |                                                                                     | -0.3 | $V_{DDIO} + 0.3$  | V     |

| Receiver input voltage                                                                                           |                                                                                     | -0.3 | $V_{DDA} + 0.3$   | V     |

| CSI-2 output voltage                                                                                             |                                                                                     | -0.3 | $V_{DDCSI} + 0.3$ | V     |

| 40L WQFN package, maxim                                                                                          | um power dissipation capacity at 25°C (derate above 25°C)                           |      | $1/R_{\theta JA}$ | mW/°C |

| Junction temperature, T <sub>J</sub>                                                                             |                                                                                     |      | 150               | °C    |

| Storage temperature, T <sub>stg</sub>                                                                            |                                                                                     | -65  | 150               | °C    |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) For soldering specifications, see product folder at www.ti.com and Absolute Maximum Ratings for Soldering (SNOA549).

## 6.2 ESD Ratings

|                                  |                                                                                  |                                                                       |                                                          | VALUE  | UNIT |

|----------------------------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------|--------|------|

| V <sub>(ESD)</sub> Electrostatic |                                                                                  | Human body model (HBM), per AEC Q                                     | 100-002, all pins <sup>(1)</sup>                         | ±8000  |      |

|                                  |                                                                                  | Charged device model (CDM), per AEC                                   | Q100-011, all pins                                       | ±1000  |      |

|                                  | Machine model (MM)                                                               | ±250                                                                  |                                                          |        |      |

|                                  | IEC, powered-up only,<br>R <sub>D</sub> = 330 $\Omega$ , C <sub>S</sub> = 150 pF | Air discharge (R <sub>IN+</sub> , R <sub>IN-</sub> )                  | ±30000                                                   |        |      |

|                                  |                                                                                  | Contact discharge (R <sub>IN+</sub> , R <sub>IN-</sub> )              | ±10000                                                   | V      |      |

|                                  | alsonarge                                                                        | ISO10605,<br>$R_D = 330 \Omega$ , $C_S = 150 pF$<br>ISO10605,         | Air discharge (R <sub>IN+</sub> , R <sub>IN-</sub> )     | ±30000 |      |

|                                  |                                                                                  |                                                                       | Contact discharge (R <sub>IN+</sub> , R <sub>IN-</sub> ) | ±10000 |      |

|                                  |                                                                                  |                                                                       | Air discharge (R <sub>IN+</sub> , R <sub>IN-</sub> )     | ±30000 |      |

|                                  |                                                                                  | $R_D = 2 \text{ k}\Omega$ , $C_S = 150 \text{ pF or } 330 \text{ pF}$ | Contact discharge (R <sub>IN+</sub> , R <sub>IN-</sub> ) | ±10000 |      |

<sup>(1)</sup> AEC Q100-002 indicates HBM stressing is done in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                          |                                |           | MIN  | NOM | MAX  | UNIT       |  |

|------------------------------------------|--------------------------------|-----------|------|-----|------|------------|--|

| $V_{DDA}, V_{DDP}, \ V_{DDL}, V_{DDCSI}$ | Supply voltage                 |           | 1.71 | 1.8 | 1.89 | V          |  |

| V                                        | LVCMOC averaly valtage         | 1.8-V I/O | 1.71 | 1.8 | 1.89 | V          |  |

| V <sub>DDIO</sub><br>PCLK                | LVCMOS supply voltage          | 3.3-V I/O | 3    | 3.3 | 3.6  |            |  |

| PCLK                                     | Clock frequency                |           | 10   |     | 75   | MHz        |  |

| $V_{DDn}$                                | Supply noise (1.8 V)           |           |      |     | 25   | $mV_{P-P}$ |  |

| V                                        | 0 1 .                          | 1.8-V I/O |      |     | 25   | 25         |  |

| 55                                       | Supply noise                   | 3.3-V I/O |      |     | 50   | $mV_{P-P}$ |  |

| T <sub>A</sub>                           | Operating free-air temperature |           | -40  | 25  | 105  | °C         |  |

#### 6.4 Thermal Information

|                      |                                              | DS90UB921Q-1 |      |

|----------------------|----------------------------------------------|--------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | RTA (WQFN)   | UNIT |

|                      |                                              | 48 PINS      |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 30.3         | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 16.4         | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 6.3          | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.2          | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 6.3          | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 2.2          | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

### 6.5 Electrical Characteristics: DC

over operating free-air temperature range (unless otherwise noted) (1)(2)(3)

|                    | PARAMETER                                       | TEST CONDIT                                                                                                           | IONS                                                                                            | MIN                      | TYP | MAX                      | UNIT |

|--------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------|-----|--------------------------|------|

| 3.3-V I/O I        | LVCMOS, V <sub>DDIO</sub> = 3 to 3.6 V (BISTEN  | I, LOCK, PASS, PDB, EQ[3:1], ID[                                                                                      | 1:0], CONFIG[1:0], G                                                                            | PIO)                     |     |                          |      |

| V <sub>IH</sub>    | High-level input voltage                        | $V_{IN} = 3 \text{ V to } 3.6 \text{ V}$                                                                              |                                                                                                 | 2.2                      |     | $V_{DDIO}$               | V    |

| V <sub>IL</sub>    | Low-level input voltage                         | V <sub>IN</sub> = 3 V to 3.6 V                                                                                        |                                                                                                 | GND                      |     | 0.8                      | V    |

| I <sub>IN</sub>    | Input current                                   | V <sub>IN</sub> = 0 V or V <sub>DDIO</sub>                                                                            |                                                                                                 | -15                      |     | 15                       | μa   |

| V <sub>OH</sub>    | High-level output voltage                       | I <sub>OH</sub> = −2 mA                                                                                               |                                                                                                 | 2.4                      |     | $V_{DDIO}$               | V    |

| V <sub>OL</sub>    | Low-level output voltage                        | I <sub>OL</sub> = 2 mA                                                                                                |                                                                                                 | GND                      |     | 0.4                      | V    |

| l <sub>oz</sub>    | TRI-STATE® output current                       | PDB = 0 V                                                                                                             |                                                                                                 | -15                      |     | 15                       | μa   |

| 1.8-V I/O I        | LVCMOS, V <sub>DDIO</sub> = 1.71 to 1.89 V (BIS | TEN, LOCK, PASS, PDB, EQ[3:1]                                                                                         | , ID[1:0], CONFIG[1:                                                                            | 0], GPIO)                |     |                          |      |

| V <sub>IH</sub>    | High-level input voltage                        | V <sub>IN</sub> = 1.71 V to 1.89 V                                                                                    |                                                                                                 | 0.65 × V <sub>DDIO</sub> |     | $V_{DDIO}$               | V    |

| V <sub>IL</sub>    | Low-level input voltage                         | V <sub>IN</sub> = 1.71 V to 1.89 V                                                                                    |                                                                                                 | GND                      |     | 0.35 × V <sub>DDIO</sub> | V    |

| I <sub>IN</sub>    | Input current                                   | V <sub>IN</sub> = 0 V or V <sub>DDIO</sub>                                                                            |                                                                                                 | -15                      |     | 15                       | μa   |

| V <sub>OH</sub>    | High-level output voltage                       | $I_{OH} = -2 \text{ mA}$                                                                                              |                                                                                                 | V <sub>DDIO</sub> - 0.45 |     | $V_{DDIO}$               | V    |

| V <sub>OL</sub>    | Low-level output voltage                        | I <sub>OL</sub> = 2 mA                                                                                                |                                                                                                 | GND                      |     | 0.45                     | V    |

| I <sub>OZ</sub>    | TRI-STATE output current                        | PDB = 0 V                                                                                                             |                                                                                                 | -15                      |     | 15                       | μa   |

| SUPPLY (           | CURRENT                                         |                                                                                                                       |                                                                                                 |                          |     |                          |      |

|                    | Ourally suggest                                 | Supply current drawn from 1.8-V rail (V <sub>DDL</sub> , V <sub>DDP</sub> , V <sub>DDA</sub> ), checker board pattern | $V_{DDL}$ , $V_{DDP}$ ,<br>$V_{DDA} = 1.89 \text{ V}$ ,<br>f = 75  MHz<br>(900 Mbps)            |                          | 88  | 95                       | mA   |

| I <sub>DD1</sub>   | Supply current                                  |                                                                                                                       | V <sub>DDL</sub> , V <sub>DDP</sub> ,<br>V <sub>DDA</sub> = 1.89 V,<br>f = 10 MHz<br>(120 Mbps) |                          | 38  |                          |      |

|                    | Correla sources                                 | Supply current drawn at                                                                                               | V <sub>DDCSI</sub> = 1.89 V,<br>f = 75 MHz<br>(900 Mbps)                                        |                          | 50  | 65                       | A    |

| I <sub>DDTX1</sub> | Supply current                                  | V <sub>DDCSI</sub> , checker board pattern                                                                            | V <sub>DDCSI</sub> = 1.89 V,<br>f = 10 MHz<br>(120 Mbps)                                        |                          | 22  |                          | mA   |

|                    | Supply ourrest                                  | Supply current drawn at                                                                                               | V <sub>DDIO</sub> = 1.89 V,<br>f = 75 MHz<br>(900 Mbps)                                         |                          |     | 10                       | mΛ   |

| I <sub>DDIO1</sub> | Supply current                                  | V <sub>DDIO</sub> , checker board pattern                                                                             | V <sub>DDIO</sub> = 3.6 V,<br>f = 75 MHz<br>(900 Mbps)                                          |                          |     | 15                       | mA   |

<sup>(1)</sup> Current into device pins is defined as positive. Current out of a device pin is defined as negative. Voltages are referenced to ground except VOD, ΔVOD, VTH and VTL which are differential voltages.

<sup>(2)</sup> Typical values represent most likely parametric norms at V<sub>DD</sub> = 3.3 V, T<sub>A</sub> = 25°C, and at the recommended operation conditions at the time of product characterization and are not ensured.

<sup>(3)</sup> The Electrical Characteristics tables list ensured specifications in *Recommended Operating Conditions* except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not ensured.

# **Electrical Characteristics: DC (continued)**

over operating free-air temperature range (unless otherwise noted) $^{(1)(2)(3)}$

|                         | PARAMETER                                       | TEST CONDITIONS                                                                                                                                                                      |                                                    | MIN         | TYP | MAX  | UNIT |

|-------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------------|-----|------|------|

| I <sub>DDZ</sub>        | Supply current at power down mode               | Supply current drawn from 1.8-V rail $V_{DDA}$ ), PDB = 0 V, $V_{DDL}$ , $V_{DDP}$ , $V_{DDA}$ : (all other LVCMOS inputs low)                                                       | (V <sub>DDL</sub> , V <sub>DDP</sub> ,<br>= 1.89 V |             |     | 5    | mA   |

| I <sub>DDTXZ</sub>      | Supply current at power down mode               | Supply current drawn at $V_{DDCSI}$ , PDB $V_{DDCSI} = 1.89 V$ (all other LVCMOS in                                                                                                  |                                                    |             |     | 5    | mA   |

| I <sub>DDIOZ</sub>      | Supply current at power down mode               | V <sub>DDIO</sub> , PDB = 0 V (all other                                                                                                                                             | = 1.89 V<br>= 3.6 V                                |             |     | 3    | mA   |

| I <sub>DDUPLS</sub>     | Ultra-low power state current                   | Supply current drawn from 1.8 V at (V $_{DDA}$ , $V_{DDCSI}$ and $V_{DDIO}$ ), $V_{DD}=1.89$ V $_{DDIO}=3.6$ V, PLL off, no change in signals, Register: $0x19h=0x03h$ $0x01h=0x02h$ | ٧,                                                 |             |     | 20   | mA   |

| FPD-LINK II F           | RECEIVER (RIN±)                                 |                                                                                                                                                                                      |                                                    |             |     |      |      |

| $V_{TH}$                | Differential input threshold high voltage       | V <sub>CM</sub> = 1.2 V (internal V <sub>BIAS</sub> )                                                                                                                                |                                                    |             |     | 50   | mV   |

| $V_{TL}$                | Differential input threshold low voltage        | V <sub>CM</sub> = 1.2 V (internal V <sub>BIAS</sub> )                                                                                                                                |                                                    | -50         |     |      | mV   |

| V <sub>CM</sub>         | Common mode voltage, internal V <sub>BIAS</sub> |                                                                                                                                                                                      |                                                    |             | 1.2 |      | V    |

| I <sub>IN</sub>         | Input current                                   | $V_{IN} = 0 \text{ V or } V_{DD}$                                                                                                                                                    |                                                    | <b>-</b> 15 |     | 15   | μa   |

| R <sub>T</sub>          | Internal termination resistor                   | Differential across RIN+ and RIN-                                                                                                                                                    |                                                    | 80          | 100 | 120  | Ω    |

| CMLOUT± DR              | RIVER OUTPUT (CMLOUT±)                          |                                                                                                                                                                                      | "                                                  |             |     |      |      |

| V <sub>OD</sub>         | Differential output voltage (4)                 | R <sub>L</sub> = 100 Ω                                                                                                                                                               |                                                    |             | 500 |      | mV   |

| Vos                     | Offset voltage, single-ended                    | R <sub>L</sub> = 100 Ω                                                                                                                                                               |                                                    |             | 1.3 |      | V    |

| R <sub>T</sub>          | Internal termination resistor                   | Differential across CMLOUT+ and CM                                                                                                                                                   | /ILOUT-                                            | 80          | 100 | 120  | Ω    |

| HSTX DRIVE              | R (DATA0±, DATA1±, CLK±)                        |                                                                                                                                                                                      |                                                    |             |     |      |      |

| V <sub>CMTX</sub>       | HS transmit static common-mode voltage          |                                                                                                                                                                                      |                                                    | 150         | 200 | 250  | mV   |

| ΔV <sub>CMTX(1,0)</sub> | VCMTX mismatch when output is 1 or 0 state      |                                                                                                                                                                                      |                                                    |             |     | 5    | mV   |

| V <sub>OD</sub>         | HS transmit differential voltage                |                                                                                                                                                                                      |                                                    | 140         | 200 | 270  | mV   |

| ΔV <sub>OD</sub>        | VOD mismatch when output is 1 or 0 state        |                                                                                                                                                                                      |                                                    |             |     | 10   | mV   |

| V <sub>OHHS</sub>       | HS output high voltage                          |                                                                                                                                                                                      |                                                    |             |     | 360  | mV   |

| Z <sub>OS</sub>         | Single ended output impedance                   |                                                                                                                                                                                      |                                                    | 40          | 50  | 62.5 | Ω    |

| $\Delta Z_{OS}$         | Mismatch in single ended output impedance       |                                                                                                                                                                                      |                                                    |             |     | 10%  |      |

| LPTX DRIVER             | R (DATA0±, DATA1±, CLK±)                        |                                                                                                                                                                                      |                                                    |             |     |      |      |

| V <sub>OH</sub>         | Output high level <sup>(5)</sup>                |                                                                                                                                                                                      |                                                    | 1.1         | 1.2 | 1.3  | V    |

| V <sub>OL</sub>         | Output low level                                |                                                                                                                                                                                      |                                                    | -50         |     | 50   | mV   |

| Z <sub>OLP</sub>        | Output impedance                                |                                                                                                                                                                                      |                                                    | 110         |     |      | Ω    |

Voltage difference compared to the DC average common mode potential. Specification is ensured by characterization.

# 6.6 Switching Characteristics: AC

over operating free-air temperature range (unless otherwise noted)

|                              | PARAMETER                                  | TEST C                                                                   | CONDITIONS                                     | MIN                                         | TYP          | MAX | UNIT               |

|------------------------------|--------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------|---------------------------------------------|--------------|-----|--------------------|

| FPD-LINK II R                | ECEIVER (RIN±)                             |                                                                          |                                                |                                             |              |     |                    |

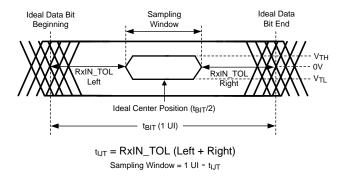

|                              | Input jitter tolerance,                    | EQ = OFF,                                                                | jitter freq < 2 MHz                            |                                             | 0.9          |     | UI <sup>(1)</sup>  |

| t <sub>IJT</sub>             | see Figure 1                               | PCLK = 65 MHz                                                            | jitter freq > 6 MHz                            |                                             | 0.5          |     | UI                 |

| t <sub>DDLT</sub>            | Deserializer lock time see Figure 2        | PCLK = 75 MHz                                                            |                                                |                                             | 10           |     | ms                 |

| HSTX DRIVER                  | R (DATA0±, DATA1±, CLK±)                   |                                                                          |                                                |                                             |              |     |                    |

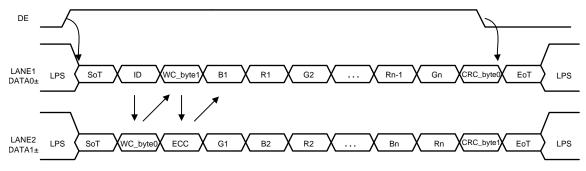

| HSTX <sub>DBR</sub>          | Data bit rate                              | DATA0±, DATA1±,<br>MHz <sup>(2)</sup>                                    | PCLK = 10 to 75                                | 120                                         | PCLK ×<br>12 | 900 | Mbps               |

| f <sub>CLK</sub>             | DDR Clock frequency                        | CLK±, PCLK = 10                                                          | to 75 MHz <sup>(2)</sup>                       | 60                                          | PCLK × 6     | 450 | MHz                |

| $\Delta V_{\text{CMTX(HF)}}$ | Common mode voltage variations HF          | Common-level vari<br>MHz <sup>(2)</sup>                                  | ations above 450                               |                                             |              | 15  | $mV_{RMS}$         |

| $\Delta V_{\text{CMTX(LF)}}$ | Common mode voltage variations LF          | Common-level vari<br>450 MHz <sup>(2)</sup>                              | ations between 50 to                           |                                             |              | 25  | $mV_{PEAK}$        |

| 4                            | Rise time HS                               | 20% to 80% rise tir                                                      | ma (3)                                         |                                             |              | 0.3 | UI <sub>INST</sub> |

| t <sub>RHS</sub>             | KISE UITIE FIS                             | 20% to 80% lise til                                                      | ne.                                            | 150                                         |              |     | ps                 |

| 4                            | Fall time HS                               | 20% to 80% rise tir                                                      | ma (3)                                         |                                             |              | 0.3 | UI <sub>INST</sub> |

| t <sub>FHS</sub>             | raii uilie no                              | 20% to 80% lise til                                                      | ile.                                           | 150                                         |              |     | ps                 |

|                              |                                            | f <sub>LPMAX</sub>                                                       |                                                |                                             |              | -18 | dB                 |

| $SDD_{TX}$                   | TX differential return loss <sup>(2)</sup> | $f_{H}$                                                                  |                                                |                                             |              | -12 | dB                 |

|                              |                                            | f <sub>MAX</sub>                                                         |                                                |                                             |              | -6  | dB                 |

| SCC <sub>TX</sub>            | TX common mode return loss <sup>(2)</sup>  | f <sub>LPMAX</sub> to f <sub>MAX</sub>                                   |                                                |                                             |              | -6  | dB                 |

| LPTX DRIVER                  | R (DATA0±, DATA1±, CLK±) <sup>(4)</sup>    |                                                                          |                                                |                                             |              |     |                    |

| t <sub>RLP</sub>             | Rise time                                  | LP 15% to 85% ris<br>C <sub>LOAD</sub> = 70 pF lum                       |                                                |                                             |              | 25  | ns                 |

| t <sub>FLP</sub>             | Fall time                                  | LP 15% to 85% fall C <sub>LOAD</sub> = 70 pF lum                         |                                                |                                             |              | 25  | ns                 |

| t <sub>REOT</sub>            | Post-EoT rise and fall time                | 30% to 85% rise tir                                                      | me and fall time <sup>(2)</sup>                |                                             |              | 35  | ns                 |

| t <sub>LP-PULSE-TX</sub>     | Pulse width of the LP exclusive-OR clock   |                                                                          | OR clock pulse after<br>ulse before Stop state | 40                                          |              |     | ns                 |

|                              |                                            | All other pulses <sup>(2)</sup>                                          |                                                | 20                                          |              |     | ns                 |

| t <sub>LP-PER-TX</sub>       | Period of the LP exclusive-OR clock (2)    |                                                                          |                                                | 90                                          |              |     | ns                 |

|                              |                                            | $C_{LOAD} = 0 pF^{(5)(4)(6)}$                                            | 5)                                             |                                             |              | 500 | mV/ns              |

|                              |                                            | $C_{LOAD} = 5 pF^{(5)(4)(6)}$                                            |                                                |                                             |              | 300 | mV/ns              |

|                              |                                            | $C_{LOAD} = 20 \text{ pF}^{(5)(4)}$                                      |                                                |                                             |              | 250 | mV/ns              |

|                              |                                            | $C_{LOAD} = 70 \text{ pF}^{(3)(4)(6)}$                                   |                                                |                                             |              | 150 | mV/ns              |

| σV/σtSR                      | Slew rate                                  | $C_{LOAD} = 0 \text{ to } 70 \text{ pF}$<br>only) $^{(3)(4)(6)(7)}$      | (falling edge                                  | 30                                          |              |     | mV/ns              |

|                              |                                            | C <sub>LOAD</sub> = 0 to 70 pF (rising edge only) <sup>(3) (4) (6)</sup> |                                                | 30                                          |              |     | mV/ns              |

|                              |                                            | $C_{LOAD} = 0$ to 70 pF (rising edge only) $^{(3)}(4)(8)(9)$             |                                                | 30 - 0.075 ×<br>(V <sub>O,INST</sub> - 700) |              |     | mV/ns              |

| C <sub>LOAD</sub>            | Load capacitance (4)                       |                                                                          |                                                | 0                                           |              | 70  | pF                 |

- (1) UI is equivalent to one serialized data bit width (1UI = 1 / 28 x PCLK). The UI scales with PCLK frequency.

- (2) Specification is ensured by design and is not tested in production.

- (3) Specification is ensured by characterization.

- (4) C<sub>LOAD</sub> includes the low-frequency equivalent transmission line capacitance. The capacitance of TX and RX are assumed to always be <10 pF. The distributed line capacitance can be up to 50 pF for a transmission line with 2-ns delay.

- (5) Specification is ensured by characterization.

- (6) Measured as average across any 50 mV segment of the output signal transition.

- (7) When the output voltage is between 400 mV and 930 mV.

- (8) Where VO,INST is the instantaneous output voltage, VDP or VDN, in millivolts.

- (9) When the output voltage is between 700 mV and 930 mV.

Submit Documentation Feedback

Copyright © 2012–2016, Texas Instruments Incorporated

# **Switching Characteristics: AC (continued)**

over operating free-air temperature range (unless otherwise noted)

|                                                     | PARAMETER                                                                                                         | TEST CONDITIONS                                              | MIN                              | TYP              | MAX                              | UNIT               |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|----------------------------------|------------------|----------------------------------|--------------------|

| DATA-CLOCK                                          | TIMING SPECIFICATIONS (DATA0±, DATA0±)                                                                            | ATA1±, CLK±)                                                 |                                  |                  |                                  |                    |

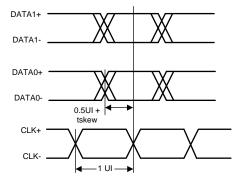

| UI <sub>INST</sub>                                  | Instantaneous unit interval, see Figure 3                                                                         | PCLK = 10 to 75 MHz <sup>(10)</sup>                          |                                  | 1/(PCLK ×<br>12) |                                  | ns                 |

| t <sub>SKEW(TX)</sub>                               | Data to clock skew see Figure 3                                                                                   | Skew between clock and data from ideal center <sup>(2)</sup> | 0.5 – 0.15                       | 0.5              | 0.5 + 0.15                       | UI <sub>INST</sub> |

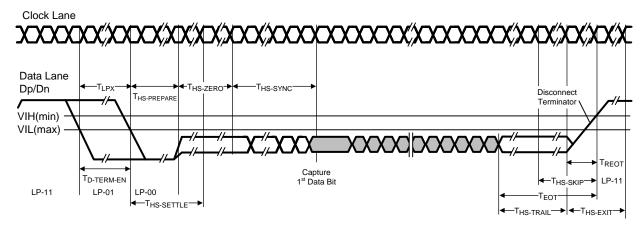

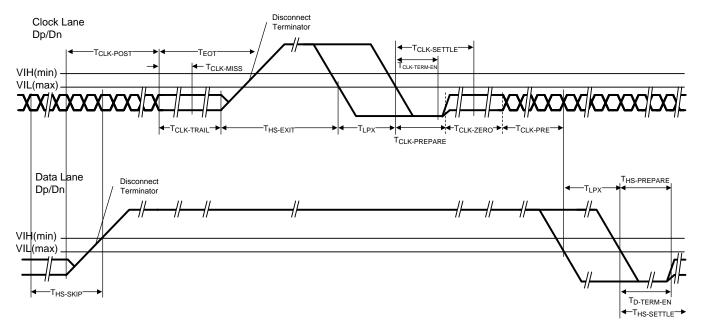

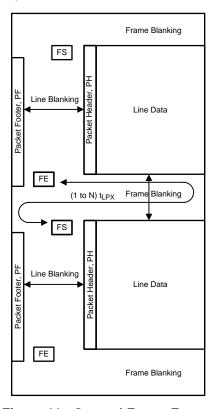

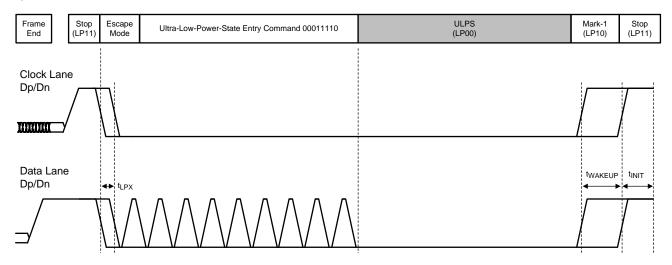

| CSI-2 TIMING                                        | SPECIFICATIONS (DATA0±, DATA1±, C                                                                                 | LK±) <sup>(2)</sup> ( see Figure 4 and Figure 5)             |                                  |                  | <u> </u>                         |                    |

| t <sub>CLK-POST</sub>                               | HS exit                                                                                                           |                                                              | 60 + 52 ×<br>UI <sub>INST</sub>  |                  |                                  | ns                 |

| t <sub>CLK-PRE</sub>                                | Time HS clock shall be driver prior to<br>any associated Data Lane beginning<br>the transition from LP to HS mode |                                                              | 8                                |                  |                                  | UI <sub>INST</sub> |

| t <sub>CLK-PREPARE</sub>                            | Clock lane HS entry                                                                                               |                                                              | 38                               |                  | 95                               | ns                 |

| t <sub>CLK-SETTLE</sub>                             | Time interval during which the HS receiver shall ignore any clock lane HS transitions                             |                                                              | 95                               |                  | 300                              | ns                 |

| t <sub>CLK-TERM-EN</sub>                            | Time-out at clock lane display module to enable HS termination                                                    |                                                              |                                  |                  | 38                               | ns                 |

| t <sub>CLK-TRAIL</sub>                              | Time that the transmitter drives the HS-0 state after the last payload clock bit of a HS transmission burst       |                                                              | 30                               |                  |                                  | ns                 |

| t <sub>CLK-PREPARE</sub> +<br>t <sub>CLK-ZERO</sub> | TCLK-PREPARE + time that the transmitter drives the HS-0 state prior to starting the clock                        |                                                              | 300                              |                  |                                  | ns                 |

| t <sub>D-TERM-EN</sub> (11)                         | Time for the data lane receiver to enable the HS line termination                                                 |                                                              | 35 + 4 × UI <sub>INST</sub>      |                  |                                  | ns                 |

| t <sub>LPX</sub>                                    | Transmitted length of LP state                                                                                    |                                                              | 50                               |                  |                                  | ns                 |

| t <sub>HS-PREPARE</sub>                             | Data lane HS entry                                                                                                |                                                              | 40 + 4 × UI <sub>INST</sub>      |                  | 85 + 6 ×<br>UI <sub>INST</sub>   | ns                 |

| t <sub>HS-PREPARE</sub> +<br>t <sub>HS-ZERO</sub>   | tHS-PREPARE + time that the transmitter drives the HS-0 state prior to transmitting the sync sequence             |                                                              | 145 + 10 ×<br>Ul <sub>INST</sub> |                  |                                  | ns                 |

| t <sub>HS-SETTLE</sub>                              | Interval HS receiver shall ignore any data lane HS transitions                                                    |                                                              | 85 + 6 × UI <sub>INST</sub>      |                  | 145 + 10 ×<br>UI <sub>INST</sub> | ns                 |

| t <sub>HS-TRAIL</sub>                               | Data lane HS exit                                                                                                 |                                                              | 60 + 4 × UI <sub>INST</sub>      |                  |                                  | ns                 |

| t <sub>EOT</sub>                                    | Transmitted time interval from the start of tHS-TRAIL to the start of the LP-11 state following a HS burst        |                                                              |                                  | ,                | 105 + 12 ×<br>UI <sub>INST</sub> | ns                 |

| t <sub>HS-EXIT</sub>                                | Time that the transmitter drives LP-11 following a HS burst.                                                      |                                                              | 100                              |                  |                                  | ns                 |

| twakeup                                             | Recovery time from ultra-low power state (ULPS)                                                                   |                                                              | 1                                |                  |                                  | ms                 |

<sup>(10)</sup> UI<sub>INST</sub> is equal to 1 / (12 x PCLK), where PCLK is the fundamental frequency for data transmission.

(11) This parameter value can be lower then TLPX due to differences in rise versus fall signal slopes and trip levels and mismatches between Dp and Dn LP transmitters. Any LP exclusive-OR pulse observed during HS EoT (transition from HS level to LP-11) is glitch behavior as described in D-PHY ver 1.00.00.

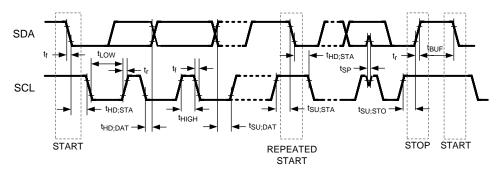

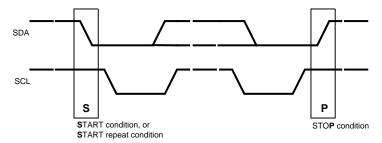

# 6.7 Timing Requirements: Serial Control Bus (CCI and I2C)

over operating free-air temperature range (unless otherwise noted; see Figure 7)(1)

|                     |                                             |               | MIN | NOM | MAX  | UNIT |

|---------------------|---------------------------------------------|---------------|-----|-----|------|------|

|                     | CCI alsolutes even even                     | Standard mode | >0  |     | 100  | kHz  |

| f <sub>SCL</sub>    | SCL clock frequency                         | Fast mode     | >0  |     | 400  | kHz  |

|                     | 001.1                                       | Standard mode | 4.7 |     |      | μs   |

| $t_{LOW}$           | SCL low period                              | Fast mode     | 1.3 |     |      | μs   |

|                     | CCI bink mariad                             | Standard mode | 4   |     |      | μs   |

| t <sub>HIGH</sub>   | SCL high period                             | Fast mode     | 0.6 |     |      | μs   |

| t <sub>HD;STA</sub> | Hold time for a start or a repeated start   | Standard mode | 4   |     |      | μs   |

|                     | condition                                   | Fast mode     | 0.6 |     |      | μs   |

| t <sub>SU;STA</sub> | Set-up time for a start or a repeated start | Standard mode | 4.7 |     |      | μs   |

|                     | condition                                   | Fast mode     | 0.6 |     |      | μs   |

| 1                   | Data hald time                              | Standard mode | 0   |     | 3.45 | μs   |

| t <sub>HD;DAT</sub> | Data hold time                              | Fast mode     | 0   |     | 0.9  | μs   |

| 1                   | Data and our time                           | Standard mode | 250 |     |      | ns   |

| t <sub>SU;DAT</sub> | Data set-up time                            | Fast mode     | 100 |     |      | ns   |

| 1                   | Cot up time for CTOR and dition             | Standard mode | 4   |     |      | μs   |

| t <sub>SU;STO</sub> | Set-up time for STOP condition              | Fast mode     | 0.6 |     |      | μs   |

| 1                   | Bus Free Time                               | Standard mode | 4.7 |     |      | μs   |

| t <sub>BµF</sub>    | between STOP and START                      | Fast mode     | 1.3 |     |      | μs   |

|                     | CCL and CDA ring time.                      | Standard mode |     |     | 1000 | ns   |

| t <sub>r</sub>      | SCL and SDA rise time                       | Fast mode     |     |     | 300  | ns   |

|                     | CCL and CDA fall time                       | Standard mode |     |     | 300  | ns   |

| t <sub>f</sub>      | SCL and SDA fall time                       | Fast mode     |     |     | 300  | ns   |

<sup>(1)</sup> Recommended Input Timing Requirements are input specifications and not tested in production.

# 6.8 Timing Requirements: DC and AC Serial Control Bus (CCI and I2C)

over operating free-air temperature range (unless otherwise noted; see Figure 7)

|                     |                          |                                                   | MIN                      | NOM                     | MAX                      | UNIT |

|---------------------|--------------------------|---------------------------------------------------|--------------------------|-------------------------|--------------------------|------|

| V <sub>IH</sub>     | Input high level voltage | SDA and SCL                                       | 0.65 × V <sub>DDIO</sub> |                         | $V_{DDIO}$               | V    |

| V <sub>IL</sub>     | Input low level voltage  | SDA and SCL                                       | GND                      |                         | 0.35 × V <sub>DDIO</sub> | V    |

|                     | la and horstone de       | Fast mode, 3.3-V I/O <sup>(1)</sup>               | 0.05 × V <sub>DDIO</sub> |                         |                          | mV   |

| V <sub>HY</sub>     | Input hysteresis         | Fast mode, 1.8 V I/O                              |                          | 0.1 × V <sub>DDIO</sub> |                          | mV   |

| V <sub>OL</sub>     | Output low level voltage | SDA, I <sub>OL</sub> = 1.5 mA                     | 0                        |                         | 0.4                      | V    |

| t <sub>R</sub>      | SDA rise time – READ     | Total capacitance of one bus line,<br>Cb ≤ 400 pF |                          |                         | 300                      | ns   |

|                     | ODA 4-11 4i DEAD         | Standard mode                                     |                          |                         | 1000                     | ns   |

| t <sub>F</sub>      | SDA fall time – READ     | Fast mode                                         |                          |                         | 300                      | ns   |

|                     | Oct on time DEAD         | Standard mode                                     | 250                      |                         |                          | ns   |

| t <sub>SU;DAT</sub> | Set-up time – READ       | Fast mode                                         | 100                      |                         |                          | ns   |

| t <sub>HD;DAT</sub> | Hold-up time – READ      |                                                   | 0                        |                         |                          | ns   |

| t <sub>SP</sub>     | Input filter             | Fast mode                                         |                          | 50                      |                          | ns   |

| C <sub>in</sub>     | Input capacitance        | SDA and SCL                                       |                          | 5                       |                          | pF   |

(1) Specification is ensured by characterization.

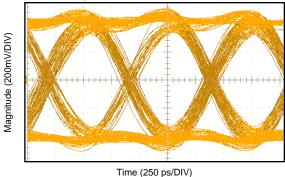

Figure 1. Receiver Input Jitter Tolerance

Figure 2. Deserializer PLL Lock Time

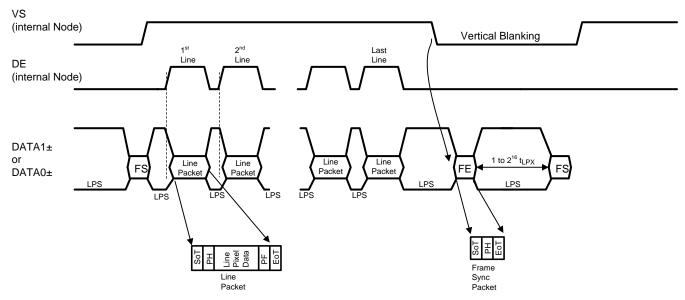

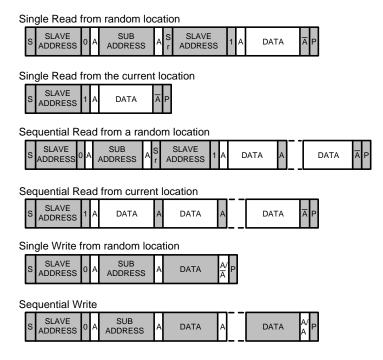

Figure 3. Clock and Data Timing in HS Transmission