LM98640QML-SP

SNAS461G -MAY 2010-REVISED NOVEMBER 2018

# LM98640QML-SP Radiation Hardness Assured (RHA), Dual Channel, 14-Bit, 40-MSPS Analog Front End With LVDS Output

#### 1 Features

- Radiation Hardened

- TID 100 krad(Si)

- Single Event Latch-Up (SEL) Immune to LET = 120 MeV-cm<sup>2</sup>/mg

- Single Event Functional Interrupt (SEFI) Free to 120 MeV-cm<sup>2</sup>/mg

- SMD 5962R1820301VXC

- ADC Resolution: 14-Bit

- ADC Sampling Rate: 5 MSPS to 40 MSPS

- Input Level: 2.85 V

- Supply Voltages 3.3 V and 1.8 V (Nominal)

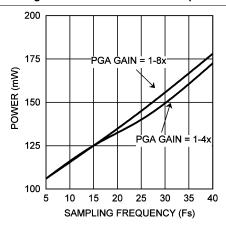

- 125 mW per Channel at 15 MSPS

- 178 mW per Channel at 40 MSPS

- CDS or S/H Processing for CCD or CIS Sensors

- CDS or S/H Gain 0 dB or 6 dB

- Programmable Analog Gain for Each Channel

- 256 Steps; Range –3 dB to 18 dB

- Programmable Analog Offset Correction

- Fine and Coarse DAC Resolution ±8 Bits

- Fine DAC Range ±5 mV

- Coarse DAC Range ±250 mV

- Programmable Input Clamp Voltage

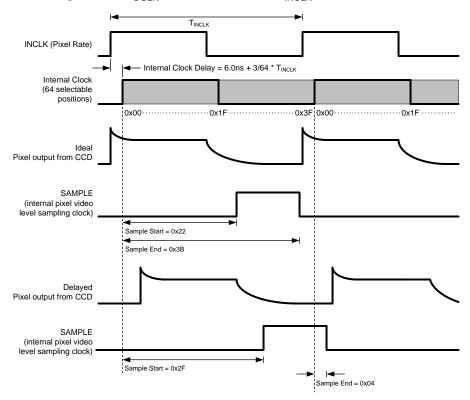

- Programmable Sample Edge: 1/64th Pixel Period

- INL at 15 MHz: ±3.5 LSB

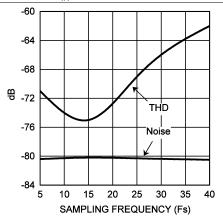

- Noise Floor: –79 dB

- Crosstalk: –80 dB

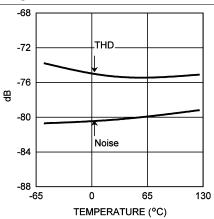

- Operating Temp: –55°C to 125°C

# 2 Applications

- Space Satellites Scientific Applications

- Focal Plane Electronics

- Imaging Attitude Control Systems

- Earth Imaging

# 3 Description

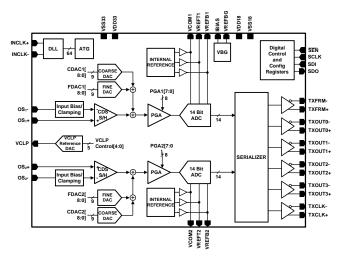

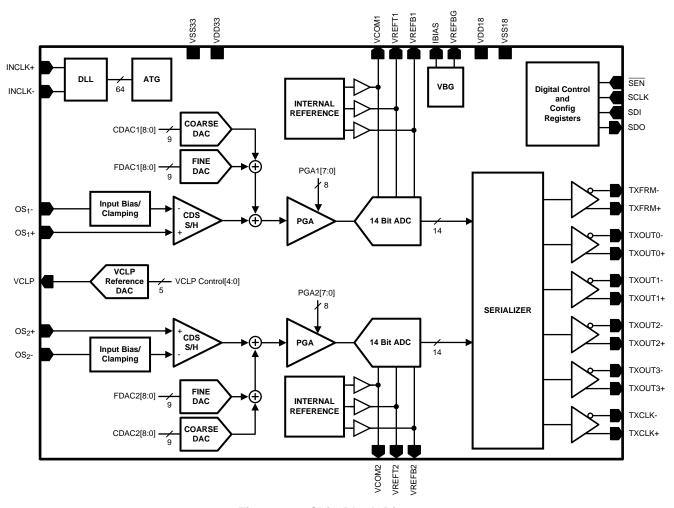

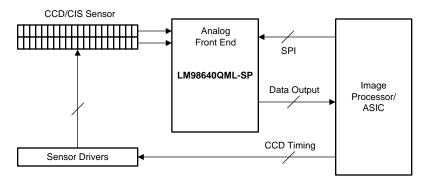

The LM98640QML-SP is a fully integrated, high performance 14-Bit, 5-MSPS to 40-MSPS signal processing solution. The Serial LVDS output format performs well during single event exposure, preventing data loss. The LM98640QML-SP has an adaptive power scaling feature to optimize power consumption based on the operating frequency and amount of gain required. High-speed signal throughput is achieved with an innovative architecture utilizing Correlated Double Sampling (CDS), typically employed with CCD arrays, or Sample and Hold (S/H) inputs (for CIS and CMOS image sensors). The sampling edges are programmable to a resolution of 1/64th of a pixel period. Both the CDS and S/H have a programmable gain of either 0 dB or 6 dB. The signal paths utilize two ±8-bit offset correction DACs for coarse and fine offset correction, and 8-bit Programmable Gain Amplifiers (PGA) that can be programmed independently for each input. The signals are then routed to two on chip 14-bit 40-MHz high performance analog-to-digital converters (ADC). The fully differential processing channel provides exceptional noise immunity, having a very low noise floor of -79 dB at 1x gain.

#### Device Information<sup>(1)</sup>

| PART NUMBER     | GRADE                                       | PACKAGE   |

|-----------------|---------------------------------------------|-----------|

| 5962R1820301VXC | QMLV RHA (SMD part)<br>[100 krad(Si)]       | CQFP (68) |

| LM98640W-MLS    | Flight RHA (non-SMD part)<br>[100 krad(Si)] | CQFP (68) |

| LM96840W-MPR    | Engineering Samples <sup>(2)</sup>          | CQFP (68) |

| LM98640CVAL     | Ceramic Evaluation Board                    | EVM       |

- (1) For all available packages, see the orderable addendum at the end of the data sheet.

- (2) These units are intended for engineering evaluation only. They are processed to a noncompliant flow. These units are not suitable for qualification, production, radiation testing or flight use. Part are not warranted for performance over the full MIL specified temperature range of -55°C to 125°C or operating life.

# **Table of Contents**

| 1 | Features 1                                    |    | 7.5 Programming                                      | . 34 |

|---|-----------------------------------------------|----|------------------------------------------------------|------|

| 2 | Applications 1                                |    | 7.6 Register Maps                                    | . 36 |

| 3 | Description 1                                 | 8  | Application and Implementation                       | . 46 |

| 4 | Revision History2                             |    | 8.1 Application Information                          | . 46 |

| 5 | Pin Configuration and Functions 4             |    | 8.2 Typical Application                              | . 47 |

| 6 | Specifications7                               |    | 8.3 Initialization Set Up                            | . 47 |

| • | 6.1 Absolute Maximum Ratings                  | 9  | Layout                                               | . 48 |

|   | 6.2 ESD Ratings                               |    | 9.1 Layout Guidelines                                | . 48 |

|   | 6.3 Recommended Operating Conditions          | 10 | Device and Documentation Support                     | . 49 |

|   | 6.4 Thermal Information 8                     |    | 10.1 Device Support                                  |      |

|   | 6.5 Quality Conformance Inspection            |    | 10.2 Receiving Notification of Documentation Updates | s 49 |

|   | 6.6 LM98640QML-SP Electrical Characteristics9 |    | 10.3 Community Resources                             | . 49 |

|   | 6.7 AC Timing Specifications                  |    | 10.4 Export Control Notice                           | . 49 |

|   | 6.8 Typical Performance Characteristics       |    | 10.5 Trademarks                                      | . 49 |

| 7 | Detailed Description                          |    | 10.6 Electrostatic Discharge Caution                 | . 49 |

| • | 7.1 Overview                                  |    | 10.7 Glossary                                        | . 49 |

|   | 7.2 Functional Block Diagram                  | 11 | Mechanical, Packaging, and Orderable                 |      |

|   | 7.3 Feature Description                       |    | Information                                          | . 50 |

|   | 7.4 Device Functional Mode                    |    | 11.1 Engineering Samples                             | . 50 |

|   | 7.1 Dovice i ariotional Mode                  |    |                                                      |      |

# 4 Revision History

| Cł | hanges from Revision F (October 2018) to Revision G                                           | Page |

|----|-----------------------------------------------------------------------------------------------|------|

| •  | Changed pin diagram in Pin Configuration and Functions section to correct typographical error | 4    |

| Cł | hanges from Revision E (December 2017) to Revision F                                          | Page |

| •  | Deleted Operating Life Test Delta Parameters Table                                            | 1    |

| •  | Updated Features section bullets to include SMD information                                   | 1    |

| •  | Updated Applications section                                                                  | 1    |

| •  | Added new orderable to the Device Information table                                           | 1    |

| •  | Added engineering samples footnote                                                            | 1    |

| •  | Deleted LM98640-MDR and LM9864-MDP from the Device Information table                          | 1    |

| •  | Updated thermal metrics                                                                       | 8    |

| •  | Deleted 15 MHz and 25 MHz min/max spec                                                        | 11   |

| •  | Changed ENOB typical for subgroup 6 at 25 MHz                                                 | 16   |

| •  | Added minimum spec value for ENOB subgroups 4,5 at 40 MHz                                     |      |

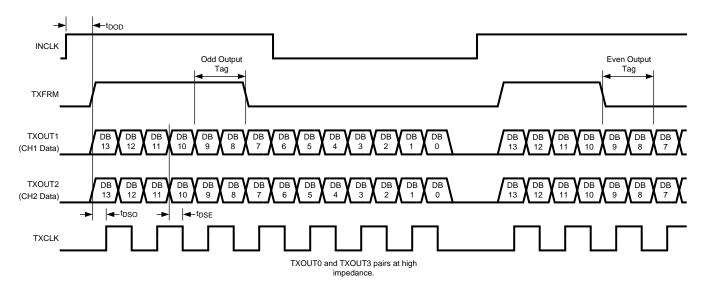

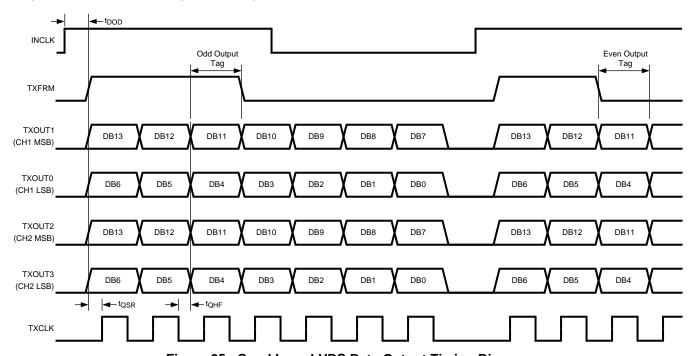

| •  | Changed pulses to windows                                                                     | 23   |

| •  | Updated wording in CDS Mode CLAMP/SAMPLE Adjust section                                       | 23   |

| •  | Updated wording in Input Bias and Clamping section                                            | 24   |

| Cł | hanges from Revision D (September 2015) to Revision E                                         | Page |

| •  | Changed 64 Lead to 68 Lead in the Device Information table                                    | 1    |

| Added, updated, or revised the following sections in accordance with new datasheet standards: Description Configuration and Functions, Specifications, Detailed Description, Application and Implementation, Power Recommendations, Layout, Device and Documentation Support, Mechanical, Packaging, and Ordering In Changed CLPIN I <sub>IH</sub> from 44 to 100 μA  Changed SEN I <sub>IH</sub> from 28 to 100 μA  Changed SEN I <sub>IL</sub> from -70 to -100 μA  Changed INCLK I <sub>IHL</sub> from 36 to 100 μA  Added mininum limits for t <sub>DSO</sub> , t <sub>DSE</sub> , t <sub>QSR</sub> and t <sub>QHF</sub> and deleted maximum limits. | wer Supply<br>g Information 1 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| Changed SEN I <sub>IH</sub> from 28 to 100 μA Changed SEN I <sub>IL</sub> from –70 to –100 μA Changed INCLK I <sub>IHL</sub> from 36 to 100 μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                               |

| Changed SEN I <sub>IL</sub> from –70 to –100 μA  Changed INCLK I <sub>IHL</sub> from 36 to 100 μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9                             |

| • Changed INCLK I <sub>IHL</sub> from 36 to 100 μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 9                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                               |

| <ul> <li>Added mininum limits for t<sub>DSO</sub>, t<sub>DSE</sub>, t<sub>QSR</sub> and t<sub>QHF</sub> and deleted maximum limits</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 9                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 17                            |

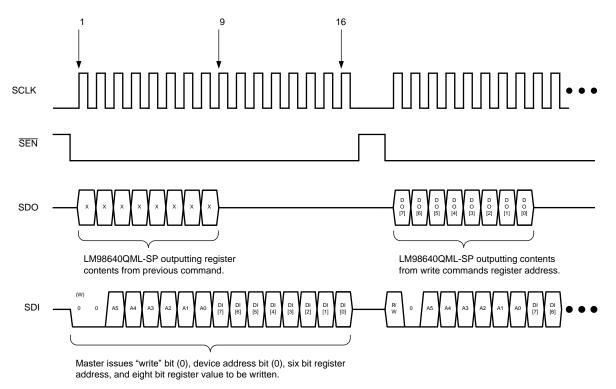

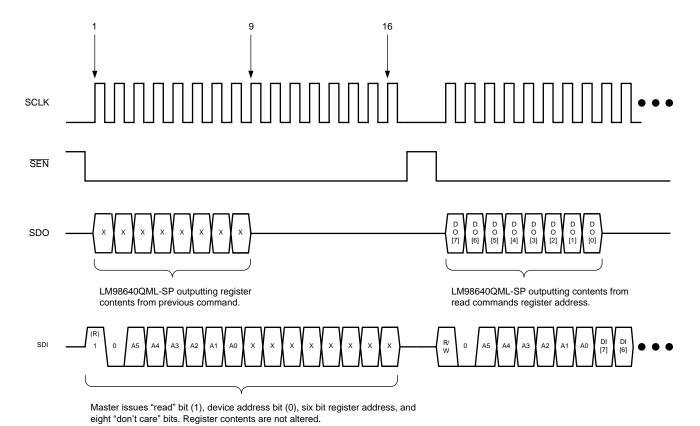

| Added details on register write.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 34                            |

| Changed Device Revision ID from x01 to x48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                               |

| Changed Device Revision ID from x01 to x48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                               |

| Added TID test and ELDRS-free information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 46                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                               |

| Changes from Revision B (January 2011) to Revision C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Page                          |

| layout of datasheet from National to TI format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1                             |

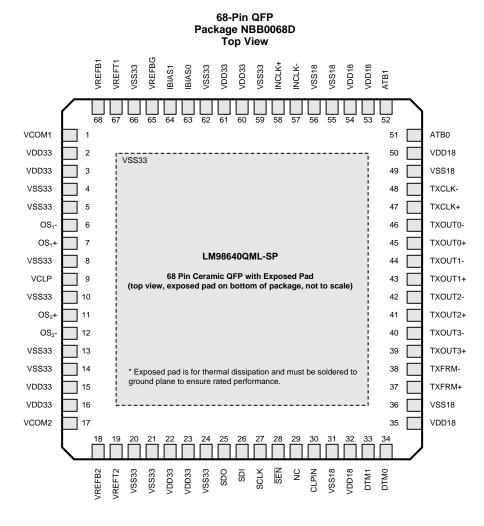

# 5 Pin Configuration and Functions

#### **Pin Functions**

| PIN | NAME           | I/O <sup>(1)</sup> | TYP    | RES | DESCRIPTION                                                                                          |  |  |  |

|-----|----------------|--------------------|--------|-----|------------------------------------------------------------------------------------------------------|--|--|--|

| 1   | VCOM1          | 0                  | Α      |     | Common mode of ADC reference. Bypass with 0.1-µF capacitor to VSS33.                                 |  |  |  |

| 2   | VDD33          |                    | Р      |     | Analog power supply. Decouple with minimum 0.1-µF capacitor to VSS33 plane.                          |  |  |  |

| 3   | VDD33          |                    | Р      |     | Analog power supply. Decouple with minimum 0.1-µF capacitor to VSS33 plane.                          |  |  |  |

| 4   | VSS33          |                    | Р      |     | Analog supply return.                                                                                |  |  |  |

| 5   | VSS33          |                    | Р      |     | Analog supply return.                                                                                |  |  |  |

| 6   | OS1-           | 1                  | Α      |     | Analog input signal.                                                                                 |  |  |  |

| 7   | OS1+           | I                  | Α      |     | Sample/Hold Mode Reference Level. Bypassed with a 0.1-µF to ground in CDS mode.                      |  |  |  |

| 8   | VSS33          |                    | Р      |     | Analog supply return.                                                                                |  |  |  |

| 9   | VCLP           | 0                  | Α      |     | Programmable Clamp Voltage output. Normally bypassed with a 0.1-µF capacitor to VSS33.               |  |  |  |

| 10  | VSS33          |                    | Р      |     | Analog supply return.                                                                                |  |  |  |

| 11  | OS2+           | 1                  | Α      |     | Sample/Hold Mode Reference Level. Bypassed with a 0.1-µF to ground in CDS mode.                      |  |  |  |

| 12  | OS2-           | I                  | Α      |     | Analog input signal.                                                                                 |  |  |  |

| 13  | VSS33          |                    | Р      |     | Analog supply return.                                                                                |  |  |  |

| 14  | VSS33          |                    | Р      |     | Analog supply return.                                                                                |  |  |  |

| 15  | VDD33          |                    | Р      |     | Analog power supply. Decouple with minimum 0.1-µF capacitor to VSS33 plane.                          |  |  |  |

| 16  | VDD33          |                    | Р      |     | Analog power supply. Decouple with minimum 0.1-µF capacitor to VSS33 plane.                          |  |  |  |

| 17  | VCOM2          | 0                  | Α      |     | Common mode of ADC reference. Bypass with 0.1-µF capacitor to ground.                                |  |  |  |

| 18  | VREFB2         | 0                  | Α      |     | Bottom of ADC reference. Bypass with a 0.1-µF capacitor to ground.                                   |  |  |  |

| 19  | VREFT2         | 0                  | Α      |     | Top of ADC reference. Bypass with a 0.1-μF capacitor to ground.                                      |  |  |  |

| 20  | VSS33          |                    | Р      |     | Analog supply return.                                                                                |  |  |  |

| 21  | VSS33          |                    | Р      |     | Analog supply return.                                                                                |  |  |  |

| 22  | VDD33          |                    | Р      |     | Analog power supply. Decouple with minimum 0.1-µF capacitor to VSS33 plane.                          |  |  |  |

| 23  | VDD33          |                    | Р      |     | Analog power supply. Decouple with minimum 0.1-µF capacitor to VSS33 plane.                          |  |  |  |

| 24  | VSS33          |                    | Р      |     | Analog supply return.                                                                                |  |  |  |

| 25  | SDO            | 0                  | D      |     | Serial Interface Data Output. (Tri-State when SEN is high)                                           |  |  |  |

| 26  | SDI            | <u> </u>           | D      |     | Serial Interface Data Input. (Tri-State when SEN is high)                                            |  |  |  |

| 27  | SCLK           | - 1                | D      | PD  | Serial Interface shift register clock. (Tri-State when SEN is high)                                  |  |  |  |

| 28  | SEN            | I                  | D      | PU  | Active-low chip enable for the Serial Interface.                                                     |  |  |  |

| 29  | NC             |                    | -      |     | No Connection. Can be connected to VSS18.                                                            |  |  |  |

| 30  | CLPIN          | I                  | D<br>P |     | Input clamp signal.                                                                                  |  |  |  |

| 31  | VSS18<br>VDD18 |                    | P      |     | Digital supply return.  Digital power supply. Decouple with minimum 0.1-µF capacitor to VSS18 plane. |  |  |  |

| 33  | DTM1           | 0                  | D      |     | Digital Timing Monitor. If not used, can be connected to VDD18 through a 10-kΩ resistor.             |  |  |  |

| 34  | DTM0           | 0                  | D      |     | Digital Timing Monitor. If not used, can be connected to VDD16 through a 10-kΩ resistor.             |  |  |  |

| 35  | VDD18          |                    | Р      |     | Digital power supply. Decouple with minimum 0.1-µF capacitor to VSS18 plane.                         |  |  |  |

| 36  | VSS18          |                    | Р      |     | Digital supply return.                                                                               |  |  |  |

| 37  | TXFRM+         | 0                  | D      |     | LVDS Frame+                                                                                          |  |  |  |

| 38  | TXFRM-         | 0                  | D      |     | LVDS Frame-                                                                                          |  |  |  |

| 39  | TXOUT3+        | 0                  | D      |     | LVDS Data Out3+                                                                                      |  |  |  |

| 40  | TXOUT3-        | 0                  | D      |     | LVDS Data Out3-                                                                                      |  |  |  |

| 41  | TXOUT2+        | 0                  | D      |     | LVDS Data Out2+                                                                                      |  |  |  |

| 42  | TXOUT2-        | 0                  | D      |     | LVDS Data Out2-                                                                                      |  |  |  |

| 43  | TXOUT1+        | 0                  | D      |     | LVDS Data Out1+                                                                                      |  |  |  |

| 44  | TXOUT1-        | 0                  | D      |     | LVDS Data Out1-                                                                                      |  |  |  |

| 45  | TXOUT0+        | 0                  | D      |     | LVDS Data Out0+                                                                                      |  |  |  |

<sup>(1) (</sup>I = Input), (O = Output), (IO = Bi-directional), (P = Power), (D = Digital), (A = Analog), (PU = Pull Up with an internal resistor), (PD = Pull Down with an internal resistor.).

# Pin Functions (continued)

| PIN | NAME    | I/O <sup>(1)</sup> | TYP | RES | DESCRIPTION                                                                                                         |  |  |

|-----|---------|--------------------|-----|-----|---------------------------------------------------------------------------------------------------------------------|--|--|

| 46  | TXOUT0- | 0                  | D   |     | LVDS Data Out0-                                                                                                     |  |  |

| 47  | TXCLK+  | 0                  | D   |     | LVDS Clock+                                                                                                         |  |  |

| 48  | TXCLK-  | 0                  | D   |     | LVDS Clock-                                                                                                         |  |  |

| 49  | VSS18   |                    | Р   |     | Digital supply return.                                                                                              |  |  |

| 50  | VDD18   |                    | Р   |     | Digital power supply. Decouple with minimum 0.1-µF capacitor to VSS18 plane.                                        |  |  |

| 51  | ATB0    | 0                  | Α   |     | Analog Test Bus. If not used, can be connected to VSS18 through a 10-kΩ resistor.                                   |  |  |

| 52  | ATB1    | 0                  | Α   |     | Analog Test Bus. If not used, can be connected to VSS18 through a 10-kΩ resistor.                                   |  |  |

| 53  | VDD18   |                    | Р   |     | Digital power supply. Decouple with minimum 0.1-µF capacitor to VSS18 plane.                                        |  |  |

| 54  | VDD18   |                    | Р   |     | gital power supply. Decouple with minimum 0.1-µF capacitor to VSS18 plane.                                          |  |  |

| 55  | VSS18   |                    | Р   |     | Digital supply return.                                                                                              |  |  |

| 56  | VSS18   |                    | Р   |     | Digital supply return.                                                                                              |  |  |

| 57  | INCLK-  | 1                  | D   |     | Clock Input. Inverting input for LVDS clocks.                                                                       |  |  |

| 58  | INCLK+  | 1                  | D   |     | Clock Input. Non-Inverting input for LVDS clocks.                                                                   |  |  |

| 59  | VSS33   |                    | Р   |     | Analog supply return.                                                                                               |  |  |

| 60  | VDD33   |                    | Р   |     | Analog power supply. Decouple with minimum 0.1-µF capacitor to VSS33 plane.                                         |  |  |

| 61  | VDD33   |                    | Р   |     | Analog power supply. Decouple with minimum 0.1-µF capacitor to VSS33 plane.                                         |  |  |

| 62  | VSS33   |                    | Р   |     | Analog supply return.                                                                                               |  |  |

| 63  | IBIAS0  | 1                  | Α   |     | Connect with external 10-k $\Omega$ 1% resistor to IBIAS1 pin.                                                      |  |  |

| 64  | IBIAS1  | 1                  | Α   |     | Connect with external 10-k $\Omega$ 1% resistor to IBIAS0 pin.                                                      |  |  |

| 65  | VREFBG  | 0                  | Α   |     | Band gap reference output. Bypass with a 0.1-µF capacitor to VSS33. Can be overdriven with external voltage source. |  |  |

| 66  | VSS33   |                    | Р   |     | Analog supply return.                                                                                               |  |  |

| 67  | VREFT1  | 0                  | Α   |     | Top of ADC reference. Bypass with a 0.1-µF capacitor to VSS33.                                                      |  |  |

| 68  | VREFB1  | 0                  | Α   |     | Bottom of ADC reference. Bypass with a 0.1-µF capacitor to VSS33.                                                   |  |  |

|     | Exp Pad |                    | Р   |     | exposed pad must be soldered to ground plane to ensure rated performance.                                           |  |  |

## 6 Specifications

# 6.1 Absolute Maximum Ratings (1)(2)

| PARAMETER                                                                  | MIN  | MAX         | UNIT |

|----------------------------------------------------------------------------|------|-------------|------|

| Supply Voltage (VDD33)                                                     |      | 4.2         | V    |

| Supply Voltage (VDD18)                                                     |      | 2.35        | V    |

| Voltage on any VDD33 Input Pin (Not to exceed 4.2 V)                       | -0.3 | VDD33 + 0.3 | V    |

| Voltage on any VDD33 Output Pin (Not to exceed 4.2 V)                      | -0.3 | VDD33 + 0.3 | V    |

| Voltage on any VDD18 Input or Output Pin (33 to 52) (Not to exceed 2.35 V) | -0.3 | VDD18 + 0.3 | V    |

| Input Current at any pin other than Supply Pins (3)                        |      | ±25         | mA   |

| Package Input Current (except Supply Pins) (3)                             |      | ±50         | mA   |

| Maximum Junction Temperature (TA)                                          |      | 150         | °C   |

| Storage Temperature                                                        | -65  | 150         | °C   |

- (1) All voltages are measured with respect to VSS = 0 V, unless otherwise specified.

- (2) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Recommended Operating Conditions indicate conditions for which the device is functional, but do not ensure specific performance limits. For ensured specifications and test conditions, see the Electrical Characteristics. The ensured specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions. Operation of the device beyond the Recommended Operating Conditions is not recommended

- (3) When the input voltage (V<sub>IN</sub>) at any pin exceeds the power supplies (V<sub>IN</sub> < VSS or V<sub>IN</sub> > VDD33), the current at that pin should be limited to 25 mA. The 50-mA maximum package input current rating limits the number of pins that can simultaneously safely exceed the power supplies with an input current of 25 mA to two.

# 6.2 ESD Ratings<sup>(1)</sup>

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (2)                         | ±2500 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(3)</sup> | ±250  | V    |

- (1) Human body model is 100-pF capacitor discharged through a 1.5-kΩ resistor. Machine model is 220-pF discharged through 0 Ω.

- (2) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 500-V HBM is possible with the necessary precautions. Pins listed as ±2500 V may actually have higher performance.

- (3) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 250-V CDM is possible with the necessary precautions. Pins listed as ±250 V may actually have higher performance.

# 6.3 Recommended Operating Conditions<sup>(1)</sup>

| PARAMETER                               | MIN         | MAX  | UNIT |

|-----------------------------------------|-------------|------|------|

| Operating Temperature (T <sub>A</sub> ) | <b>–</b> 55 | 125  | °C   |

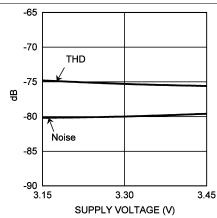

| VDD33 <sup>(2)(3)</sup>                 | 3.15        | 3.45 | V    |

| VDD18 <sup>(2)(3)</sup>                 | 1.7         | 1.9  | V    |

| VSS33 - VSS18                           |             | 100  | mV   |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not ensure specific performance limits. For ensured specifications and test conditions, see the Electrical Characteristics. The ensured specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions. Operation of the device beyond the Operating Ratings is not recommended.

- (2) All voltages are measured with respect to VSS = 0 V, unless otherwise specified.

- (3) When the input voltage (V<sub>IN</sub>) at any pin exceeds the power supplies (V<sub>IN</sub> < VSS or V<sub>IN</sub> > VDD33), the current at that pin should be limited to 25 mA. The 50-mA maximum package input current rating limits the number of pins that can simultaneously safely exceed the power supplies with an input current of 25 mA to two.

# 6.4 Thermal Information<sup>(1)</sup>

|                         |                                              | LM98640QML-SP |      |

|-------------------------|----------------------------------------------|---------------|------|

|                         | THERMAL METRIC (2)                           | NBB (CFP)     | UNIT |

|                         |                                              | 68 PINS       |      |

| $R_{\theta JA}$         | Junction-to-ambient thermal resistance       | 16.4          |      |

| $R_{\theta JC(top)}$    | Junction-to-case (top) thermal resistance    | 3.8           |      |

| $R_{\theta JB}$         | Junction-to-board thermal resistance         | 7.6           | °C/W |

| ΨЈТ                     | Junction-to-top characterization parameter   | 1.7           | C/VV |

| ΨЈВ                     | Junction-to-board characterization parameter | 7.2           |      |

| $R_{\theta JC(bottom)}$ | Junction-to-case (bottom) thermal resistance | 0.3           |      |

<sup>(1)</sup> The maximum power dissipation must be derated at elevated temperatures and is dictated by T<sub>JMAX</sub>, θ<sub>JA</sub> and the ambient temperature, T<sub>A</sub>. The maximum allowable power dissipation at any temperature is P<sub>D</sub> = (T<sup>JMAX</sup> – T<sub>A</sub>) / θ<sub>JA</sub>. The values for maximum power dissipation listed above will be reached only when the device is operated in a severe fault condition (e.g. when input or output pins are driven beyond the power supply voltages, or the power supply polarity is reversed). Such conditions should always be avoided

(2) For more information about traditional and new thermal metrics, see the *IC Package Thermal Metrics* application report, SPRA953.

## 6.5 Quality Conformance Inspection

MIL-STD-883, Method 5005 - Group A

| SUBGROUP | DESCRIPTION         | TEMP (°C) |

|----------|---------------------|-----------|

| 1        | Static tests at     | 25        |

| 2        | Static tests at     | 125       |

| 3        | Static tests at     | -55       |

| 4        | Dynamic tests at    | 25        |

| 5        | Dynamic tests at    | 125       |

| 6        | Dynamic tests at    | -55       |

| 7        | Functional tests at | 25        |

| 8A       | Functional tests at | 125       |

| 8B       | Functional tests at | -55       |

| 9        | Switching tests at  | 25        |

| 10       | Switching tests at  | 125       |

| 11       | Switching tests at  | -55       |

| 12       | Setting time at     | 25        |

| 13       | Setting time at     | 125       |

| 14       | Setting time at     | -55       |

# 6.6 LM98640QML-SP Electrical Characteristics (1)(2)

The following specifications apply for VDD33 = 3.3 V, VDD18 = 1.8 V,  $C_L$  = 10 pF, and  $f_{INCLK}$  = 40 MHz unless otherwise specified.

|                                          | PARAMETER                                | TEST CONDITIONS                                              | NOTES   | SUB-<br>GROUPS | MIN  | TYP <sup>(3)</sup> | MAX | UNIT |

|------------------------------------------|------------------------------------------|--------------------------------------------------------------|---------|----------------|------|--------------------|-----|------|

| CMOS DI                                  | GITAL INPUT DC SPECIFICATIONS (          | SCLK, SEN, SDI, CLPIN)                                       | '       |                |      |                    |     |      |

| V <sub>IH</sub>                          | Logical "1" Input Voltage                |                                                              |         | 1, 2, 3        | 2.0  |                    |     | V    |

| V <sub>IL</sub>                          | Logical "0" Input Voltage                |                                                              |         | 1, 2, 3        |      |                    | 0.8 | V    |

|                                          |                                          | CLPIN                                                        |         |                |      | 70                 | 100 | μΑ   |

| I <sub>IH</sub>                          | Logical "1" Input Current VIH = VDD33    | SCLK, SDI                                                    |         | 1, 2, 3        |      | 40                 | 300 | nA   |

|                                          | VIH = VB200                              | SEN                                                          |         |                |      | 0.2                | 6   | μΑ   |

| Logical "0" Input Current $V_{II} = VSS$ |                                          | CLPIN                                                        |         |                | -300 | -85                |     | nA   |

|                                          | SCLK, SDI                                |                                                              | 1, 2, 3 | -300           | -50  |                    | nA  |      |

| V <sub>IL</sub> = VOC                    |                                          | SEN                                                          |         |                | -100 | -70                |     | μА   |

| CMOS DI                                  | GITAL OUTPUT DC SPECIFICATION            | S (SDO)                                                      |         |                |      |                    |     | •    |

| V <sub>OH</sub>                          | Logical "1" Output Voltage               | $I_{OUT} = -0.5 \text{ mA}$                                  |         | 1, 2, 3        | 1.8  | 1.93               |     | V    |

| V <sub>OL</sub>                          | Logical "0" Output Voltage               | I <sub>OUT</sub> = 1.6 mA                                    |         | 1, 2, 3        |      | 0.05               | 0.2 | V    |

| I <sub>OH</sub>                          | Output Leakage Current                   | $V_{OUT} = V_{DD}$                                           |         | 1, 2, 3        |      | 20                 | 50  | nA   |

| I <sub>OL</sub>                          | Output Leakage Current                   | V <sub>OUT</sub> = V <sub>SS</sub>                           |         | 1, 2, 3        | -50  | -20                |     | nA   |

| LVDS CL                                  | OCK RECEIVER DC SPECIFICATION            | S (INCLK+ and INCLK- Pins)                                   |         |                |      |                    |     | •    |

|                                          | Differential LVDS Clock                  | R <sub>L</sub> = 100 Ω                                       |         |                |      |                    |     |      |

| $V_{IHL}$                                | High Threshold Voltage                   | V <sub>CM</sub> (LVDS Input Common<br>Mode Voltage) = 1.25 V |         | 1, 2, 3        |      | 100                | 250 | mV   |

|                                          | Differential LVDS Clock                  | RL = 100 Ω                                                   |         |                |      |                    |     |      |

| $V_{ILL}$                                | Low Threshold Voltage                    | V <sub>CM</sub> (LVDS Input Common<br>Mode Voltage) = 1.25 V |         | 1, 2, 3        | -250 | -100               |     | mV   |

| I <sub>IHL</sub>                         | Differential LVDS Clock Input<br>Current | V <sub>IH</sub> = VDD33                                      |         | 1, 2, 3        |      | 70                 | 100 | μА   |

| I <sub>ILL</sub>                         | Differential LVDS Clock Input<br>Current | V <sub>IL</sub> = VSS                                        |         | 1, 2, 3        | -49  | -34                |     | μА   |

(1) The analog inputs are protected as shown below. Input voltage magnitudes beyond the supply rails will not damage the device, provided the current is limited per Note 2 under the LM98640QML-SP Electrical Characteristics<sup>(1)(2)</sup>. However, input errors will be generated If the

input goes above VDD33 and below VSS. AGN

- (2) When the input voltage (V<sub>IN</sub>) at any pin exceeds the power supplies (V<sub>IN</sub> < VSS or V<sub>IN</sub> > VDD33), the current at that pin should be limited to 25 mA. The 50-mA maximum package input current rating limits the number of pins that can simultaneously safely exceed the power supplies with an input current of 25 mA to two.

- (3) Typical figures are at T<sub>A</sub> = 25°C, and represent most likely parametric norms at the time of product characterization. The typical specifications are not ensured.

# LM98640QML-SP Electrical Characteristics<sup>(1)(2)</sup> (continued)

The following specifications apply for VDD33 = 3.3 V, VDD18 = 1.8 V,  $C_L$  = 10 pF, and  $f_{INCLK}$  = 40 MHz unless otherwise specified.

|                 | PARAMETER                    | TEST CONDITIONS                           | NOTES | SUB-<br>GROUPS | MIN  | TYP <sup>(3)</sup> | MAX | UNIT |

|-----------------|------------------------------|-------------------------------------------|-------|----------------|------|--------------------|-----|------|

| LVDS OL         | JTPUT DC SPECIFICATIONS      |                                           |       |                |      |                    |     |      |

| V <sub>OD</sub> | Differential Output Voltage  | LVDS Output Modes =                       |       | 1, 2, 3        | 210  | 275                | 410 | mV   |

| Vos             | LVDS Output Offset Voltage   | 0000 x100<br>R <sub>L</sub> = 100 Ω       |       | 1, 2, 3        | 1.05 | 1.19               | 1.3 | V    |

| $V_{OD}$        | Differential Output Voltage  | LVDS Output Modes =                       |       | 1, 2, 3        | 250  | 325                | 460 | mV   |

| Vos             | LVDS Output Offset Voltage   | $0000 	ext{ x}101$ $R_L = 100 	ext{ } Ω$  |       | 1, 2, 3        | 1.05 | 1.19               | 1.3 | V    |

| V <sub>OD</sub> | Differential Output Voltage  | LVDS Output Modes =                       |       | 1, 2, 3        | 300  | 377                | 535 | mV   |

| Vos             | LVDS Output Offset Voltage   | $R_L = 100 \Omega$                        |       | 1, 2, 3        | 0.95 | 1.1                | 1.2 | V    |

| V <sub>OD</sub> | Differential Output Voltage  | LVDS Output Modes =                       |       | 1, 2, 3        | 350  | 425                | 590 | mV   |

| Vos             | LVDS Output Offset Voltage   | $R_L = 100 Ω$                             |       | 1, 2, 3        | 0.95 | 1.1                | 1.2 | V    |

| I <sub>OH</sub> | LVDS Output Leakage Current  |                                           |       | 1, 2, 3        |      | 4.25               | 5   | μΑ   |

| I <sub>OL</sub> | LVDS Output Leakage Current  |                                           |       | 1, 2, 3        | -5   | -4.29              |     | μΑ   |

| Ios             | Output Short Circuit Current | $V_{OUT} = 0 \text{ V}, R_L = 100 \Omega$ |       | 1, 2, 3        |      | 40                 | 50  | mA   |

# LM98640QML-SP Electrical Characteristics(1)(2) (continued)

The following specifications apply for VDD33 = 3.3 V, VDD18 = 1.8 V,  $C_L$  = 10 pF, and  $f_{INCLK}$  = 40 MHz unless otherwise specified.

|            | PARAMETER                                        | TEST CONDITIONS                                                | NOTES     | SUB-<br>GROUPS | MIN TYP(3)     | MAX  | UNIT                                             |

|------------|--------------------------------------------------|----------------------------------------------------------------|-----------|----------------|----------------|------|--------------------------------------------------|

| POWER SUPP | LY SPECIFICATIONS (see Power                     | Trimming section for PGA and                                   | ADC Power | Trimming reg   | ster settings) |      |                                                  |

|            |                                                  | Powerdown Control Reg<br>= 0x00                                |           |                |                |      |                                                  |

|            | VDD33 Analog Supply Current <b>Dual Channel</b>  | 5 MHz                                                          |           | 1, 2, 3        | 51.5           | 58   |                                                  |

|            | Power optimized for                              | 15 MHz                                                         |           |                | 61.3           |      | mA mA mA mA                                      |

|            | PGA Gain = 1-4x                                  | 25 MHz                                                         |           |                | 69.6           |      | mA                                               |

|            |                                                  | 40 MHz                                                         |           | 1, 2, 3        | 87.6           | 98   |                                                  |

|            |                                                  | Powerdown Control Reg<br>= 0x00                                |           |                |                |      |                                                  |

|            | VDD33 Analog Supply Current <b>Dual Channel</b>  | 5 MHz                                                          |           | 1, 2, 3        | 51.5           | 58   |                                                  |

|            | Power optimized for                              | 15 MHz                                                         |           |                | 61.3           |      |                                                  |

|            | PGA Gain = 1-8x                                  | 25 MHz                                                         |           |                | 72.9           |      | mA                                               |

|            |                                                  | 40 MHz                                                         |           | 1, 2, 3        | 91.3           | 103  |                                                  |

| IA         | VDD33 Analog Supply Current                      | Powerdown Control Reg<br>= 0x15 (CH1 PD) or<br>= 0x2A (CH2 PD) |           |                |                |      |                                                  |

|            | Single Channel                                   | 5 MHz                                                          |           | 1, 2, 3        | 29.5           | 35   |                                                  |

|            | Power optimized for PGA Gain = 1-4x              | 15 MHz                                                         |           |                | 36.1           |      | mA                                               |

|            | PGA Gain = 1-4x                                  | 25 MHz                                                         |           |                | 42             | m/   | mA                                               |

|            |                                                  | 40 MHz                                                         |           | 1, 2, 3        | 53.7           | 60   | -                                                |

|            | VDD33 Analog Supply Current                      | Powerdown Control Reg<br>= 0x15 (CH1 PD) or<br>= 0x2A (CH2 PD) |           |                |                |      | mA  335 mA  600  355 mA  644  355 mA  mA  299 mA |

|            | Single Channel                                   | 5 MHz                                                          |           | 1, 2, 3        | 29.5           | 35   |                                                  |

|            | Power optimized for PGA Gain = 1-8x              | 15 MHz                                                         |           |                | 36.1           |      |                                                  |

|            | rga Gaiii = 1-6x                                 | 25 MHz                                                         |           |                | 43.8           |      | mA                                               |

|            |                                                  | 40 MHz                                                         |           | 1, 2, 3        | 55.6           | 64   |                                                  |

|            | VDD33 Analog Supply Current <b>Powerdown</b>     | Powerdown Control Reg<br>= 0x80                                |           | 1, 2, 3        | 2.85           | 3.85 | mA                                               |

|            | VDD10 Digital Comply Correct                     | 5 MHz                                                          |           |                | 36             |      |                                                  |

|            | VDD18 Digital Supply Current LVDS Quad Lane Mode | 15 MHz                                                         |           |                | 39             |      | A                                                |

|            | LVDS Output Mode Reg<br>= 0x0E                   | 25 MHz                                                         |           |                | 42             |      | mA                                               |

|            | = UXUE                                           | 40 MHz                                                         |           |                | 45             |      |                                                  |

| ID         |                                                  | 5 MHz                                                          |           | 1, 2, 3        | 23.5           | 29   |                                                  |

|            | VDD18 Digital Supply Current                     | 15 MHz                                                         |           |                | 25.5           |      | m Λ                                              |

|            | VDD 18 Digital Supply Current                    | 25 MHz                                                         |           |                | 27.5           |      | IIIA                                             |

|            |                                                  | 40 MHz                                                         |           | 1, 2, 3        | 30.5           | 37   |                                                  |

|            | VDD18 Digital Supply Current <b>Powerdown</b>    | Powerdown Control<br>Reg = 0x80                                |           | 1, 2, 3        | 1.2            | 3.0  | mA                                               |

|            | Average Power Dissipation                        | 5 MHz                                                          |           | 1, 2, 3        | 212            | 244  |                                                  |

|            | Power optimized for PGA Gain = 1-4x              | 15 MHz                                                         |           |                | 250            |      | mW                                               |

|            | Dual Channel                                     | 25 MHz                                                         |           |                | 280            |      | 11144                                            |

| PWR        | LVDS Dual Lane Mode                              | 40 MHz                                                         |           | 1, 2, 3        | 345            | 390  |                                                  |

| I VVIX     | Average Power Dissipation                        | 5 MHz                                                          |           | 1, 2, 3        | 212            | 244  |                                                  |

|            | Power optimized for PGA Gain = 1-8x              | 15 MHz                                                         |           |                | 250            |      | mW                                               |

|            | Dual Channel                                     | 25 MHz                                                         |           |                | 290            |      | IIIVV                                            |

|            | LVDS Dual Lane Mode                              | 40 MHz                                                         |           | 1, 2, 3        | 356            | 407  |                                                  |

# LM98640QML-SP Electrical Characteristics<sup>(1)(2)</sup> (continued)

The following specifications apply for VDD33 = 3.3 V, VDD18 = 1.8 V,  $C_L$  = 10 pF, and  $f_{INCLK}$  = 40 MHz unless otherwise specified.

|                     | PARAMETER                                   | TEST CONDITIONS                | NOTES              | SUB-<br>GROUPS | MIN TYP(3)      | MAX | UNIT |

|---------------------|---------------------------------------------|--------------------------------|--------------------|----------------|-----------------|-----|------|

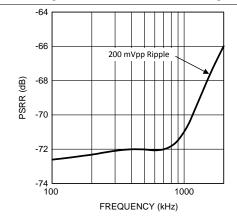

|                     |                                             | 200 mVpp, 200 KHz              |                    |                | -72.3           |     |      |

|                     | Dynamic Power Supply Rejection              | 200 mVpp, 500 KHz              |                    |                | -72             |     |      |

| PSRR                | Ratio<br>CDS Gain = 1x                      | 200 mVpp, 1 MHz                | See <sup>(4)</sup> |                | -71             |     | dB   |

|                     | PGA Gain = 1x                               | 200 mVpp, 1.5 MHz              |                    |                | -68             |     |      |

|                     |                                             | 200 mVpp, 2 MHz                |                    |                | -66             |     |      |

| INTERNAL            | REFERENCE SPECIFICATIONS                    |                                |                    |                |                 |     | •    |

| V <sub>REFBG</sub>  | Reference Voltage                           |                                | See <sup>(5)</sup> |                | 1.218           |     | V    |

|                     | Reference Tolerance (chip to chip)          |                                | See <sup>(5)</sup> |                | ±2%             |     |      |

| R <sub>REFBG</sub>  | Reference Impedance                         |                                | See <sup>(5)</sup> |                | 20              |     | kΩ   |

| V                   | Tanana watuun Cantiiniant                   | 25°C to 125°C                  |                    |                | 80              |     | ppm/ |

| V <sub>REFTC</sub>  | Temperature Coefficient                     | -55°C to 25°C                  |                    |                | 50              |     | , c  |

| INPUT SAM           | IPLING CIRCUIT SPECIFICATIONS               |                                |                    |                |                 |     | •    |

|                     |                                             | CDS Gain = 1x, PGA Gain = 1x   |                    | 4.0.0          |                 | 2   |      |

| V <sub>IN</sub>     | Input Voltage Level                         | CDS Gain = 2x, PGA Gain= 1     |                    | 1, 2, 3        |                 | 1   | Vp-p |

|                     |                                             | CDS Gain = 1x, PGA Gain = 0.7x |                    |                | 2.85            |     |      |

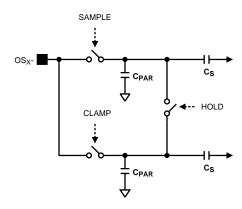

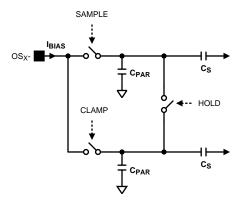

| V <sub>RESET</sub>  | Reset Feed Through                          |                                |                    |                | 500             |     | mV   |

|                     |                                             | CDS Gain = 1x                  | See <sup>(5)</sup> |                | 004             |     |      |

|                     | Sample and Hold Mode                        | $OS_X = VDD33 (OS_X = VSS)$    | See                |                | 384             |     | μΑ   |

| I <sub>IN_SH</sub>  | Input Leakage Current                       | CDS Gain = 2x                  | See <sup>(5)</sup> |                | 475             |     |      |

|                     |                                             | $OS_X = VDD33 (OS_X = VSS)$    | See                |                | <del>-475</del> |     | μA   |

|                     | Sample/Hold Mode                            | CDS Gain = 1x                  | See <sup>(5)</sup> |                | 4               |     | ~F   |

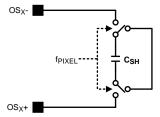

| C <sub>SH</sub>     | Equivalent Input Capacitance                | CDS Gain = 1x                  | See                |                | 4               |     | pF   |

|                     | (see Figure 20)                             | CDS Gain = 2x                  | See <sup>(5)</sup> |                | 8               |     | pF   |

|                     | CDS Mode                                    | 00 1/0000 (00 1/00)            | See <sup>(5)</sup> |                | 200             |     | ^    |

| I <sub>IN_CDS</sub> | Input Leakage Current                       | $OS_X = VDD33 (OS_X = VSS)$    | See                |                | 300             |     | nA   |

| D                   | CLPIN Switch Resistance                     |                                | See <sup>(5)</sup> |                | 16              |     | 0    |

| R <sub>CLPIN</sub>  | (OS <sub>X</sub> to VCLP Node in Figure 17) |                                | See (%)            |                | 16              |     | Ω    |

<sup>(4)</sup> Dynamic Power Supply Rejection Ratio is performed by injecting a 200-mVpp sine wave ac coupled to the analog supply pin. The LM98640QML-SP inputs are left floating in CDS mode and an FFT is captured. The spur ensured by the injected signal is recorded.

<sup>(5)</sup> This parameter is ensured by design and/or characterization and is not tested.

# LM98640QML-SP Electrical Characteristics(1)(2) (continued)

The following specifications apply for VDD33 = 3.3 V, VDD18 = 1.8 V,  $C_L$  = 10 pF, and  $f_{INCLK}$  = 40 MHz unless otherwise specified.

|                 | PARAMETER                              | TEST CONDITIONS            | NOTES | SUB-<br>GROUPS | MIN         | TYP <sup>(3)</sup> | MAX   | UNIT |

|-----------------|----------------------------------------|----------------------------|-------|----------------|-------------|--------------------|-------|------|

| VCLP REF        | FERENCE CIRCUIT SPECIFICATION          |                            |       |                |             |                    |       |      |

|                 | VCLP DAC Resolution                    |                            |       | 1, 2, 3        | 5           | 5                  |       | Bits |

|                 | VCLP DAC Step Size                     |                            |       | 1, 2, 3        | 96          | 98                 | 102   | mV   |

|                 | VCLD DAG Valta as Miss Outrout         | VCLP Control Register =    |       | 4.0.0          | 404         | 004                | 200   |      |

| V               | VCLP DAC Voltage Min Output            | 0110 0000                  |       | 1, 2, 3        | 194         | 224                | 298   | mv   |

| $V_{VCLP}$      | VCL B DAC Voltage May Output           | VCLP Control Register =    |       | 100            | 4 0 0 0 000 | 3.07 3.11          | \/    |      |

|                 | VCLP DAC Voltage Max Output            | 0111 1101                  |       | 1, 2, 3        | 2.99        |                    | 3.11  | V    |

|                 | VCLP DAC Short Circuit Output          | VCLP Control Register =    |       |                |             | 33                 |       | A    |

| I <sub>SC</sub> | Current                                | 011x xxxx                  |       |                |             | 33                 |       | mA   |

| COARSE          | ANALOG OFFSET DAC SPECIFICAT           | IONS                       |       |                |             |                    |       |      |

|                 | Resolution                             |                            |       |                |             | ±8                 |       | Bits |

|                 | Offset Adjustment Range                | Minimum DAC Code = 0x000   |       |                | -264        | -262               | -251  |      |

|                 | Referred to AFE Input<br>CDS Gain = 1x | Maximum DAC Code = 0x1FF   |       | 1, 2, 3        | 251         | 263                | 266   | mV   |

|                 | Offset Adjustment Range                | Minimum DAC Code = 0x000   |       |                | -132        | -131               | -126  |      |

|                 | Referred to AFE Input<br>CDS Gain = 2x | Maximum DAC Code = 0x1FF   |       | 1, 2, 3        | 126         | 131                | 133   | mV   |

|                 | Offset Adjustment Range                | Minimum DAC Code = 0x000   |       |                | -2162       | -2146              | -2058 |      |

|                 | Referred to AFE Output                 | Maximum DAC Code = 0x1FF   |       | 1, 2, 3        | 2058        | 2154               | 2176  | LSB  |

|                 | DAC Step Size<br>CDS Gain = 1x         | Input Referred             |       |                |             | 1                  |       | mV   |

|                 | DAC Step Size<br>CDS Gain = 1x         | Output Referred            |       |                |             | 8                  |       | LSB  |

| DNL             | Differential Non-Linearity             | CDS Gain = 1x or 2x 40 MHz |       | 1, 2, 3        | -1.1        | ±0.97              | 1.1   | LSB  |

| INL             | Integral Non-Linearity                 | CDS Gain = 1x or 2x 40 MHz |       | 1, 2, 3        | -2.8        | ±1.5               | 2.80  | LSB  |

| FINE ANA        | LOG OFFSET DAC SPECIFICATIONS          | 3                          |       |                |             |                    |       |      |

|                 | Resolution                             |                            |       |                |             | ±8                 |       | Bits |

|                 | Offset Adjustment Range                | Minimum DAC Code = 0x000   |       |                | -5.9        | -4.6               | -3.1  |      |

|                 | Referred to AFE Input<br>CDS Gain = 1x | Maximum DAC Code = 0x1FF   |       | 1, 2, 3        | 4.3         | 5.3                | 6.8   | mV   |

|                 | Offset Adjustment Range                | Minimum DAC Code = 0x000   |       |                | -2.9        | -2.3               | -1.5  |      |

|                 | Referred to AFE Input<br>CDS Gain = 2x | Maximum DAC Code = 0x1FF   |       | 1, 2, 3        | 2.1         | 2.6                | 3.4   | mV   |

|                 | Offset Adjustment Range                | Minimum DAC Code = 0x000   |       |                | -48         | -38                | -25   |      |

|                 | Referred to AFE Output                 | Maximum DAC Code = 0x1FF   |       | 1, 2, 3        | 35          | 43                 | 56    | LSB  |

|                 | DAC Step Size<br>CDS Gain = 1x         | Input Referred             |       |                |             | 20                 |       | uV   |

|                 | DAC Step Size<br>CDS Gain = 1x         | Output Referred            |       |                |             | 0.16               |       | LSB  |

| DNL             | Differential Non-Linearity             |                            |       |                |             | ±1                 |       | LSB  |

| INL             | Integral Non-Linearity                 |                            |       |                |             | ±2.2               |       | LSB  |

# LM98640QML-SP Electrical Characteristics<sup>(1)(2)</sup> (continued)

The following specifications apply for VDD33 = 3.3 V, VDD18 = 1.8 V,  $C_L$  = 10 pF, and  $f_{INCLK}$  = 40 MHz unless otherwise specified.

|                                       | PARAMETER                      | TEST CONDITIONS              | NOTES              | SUB-<br>GROUPS | MIN   | TYP <sup>(3)</sup> | MAX   | UNIT                   |

|---------------------------------------|--------------------------------|------------------------------|--------------------|----------------|-------|--------------------|-------|------------------------|

| PGA SPECIFIC                          | CATIONS                        | ·                            |                    |                | •     |                    |       | •                      |

|                                       | Gain Resolution                |                              |                    | 1, 2, 3        |       |                    | 8     | Bits                   |

|                                       | Monotonicity                   |                              | See <sup>(5)</sup> |                |       |                    |       |                        |

|                                       | Marrian Cain                   | CDS Gain = 1x                |                    | 1, 2, 3        | 7.92  | 8.3                | 8.78  | V/V                    |

|                                       | Maximum Gain                   | CDS Gain = 1x                |                    | 1, 2, 3        | 17.99 | 18.4               | 18.88 | dB                     |

|                                       | Minimum Cain                   | CDS Gain = 1x                |                    | 1, 2, 3        | 0.62  | 0.64               | 0.66  | V/V                    |

|                                       | Minimum Gain                   | CDS Gain = 1x                |                    | 1, 2, 3        | -4.15 | -3.8               | -3.54 | dB                     |

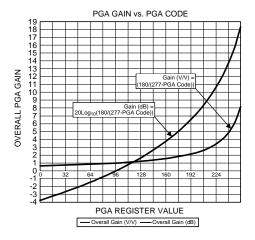

|                                       | DOA 5                          | Gain (V/V) = (180/(277-PGA C | Code))             |                |       |                    |       |                        |

|                                       | PGA Function                   | Gain (dB) = 20LOG10(180/(27  | 7-PGA Code         | e))            |       |                    |       |                        |

|                                       | Channel Matching               | M                            |                    | 1, 2           | 95.2% | 99.0%              |       |                        |

|                                       |                                | Minimum PGA Gain             |                    | 3              | 94.0% | 99.0%              |       |                        |

|                                       |                                | M : BOA O :                  |                    | 1, 2           | 95.2% | 99.0%              |       |                        |

|                                       |                                | Maximum PGA Gain             |                    | 3              | 94.0% | 99.0%              |       |                        |

| ADC SPECIFIC                          | CATIONS                        |                              | "                  |                |       |                    |       |                        |

| V <sub>REFT</sub>                     | Top of Reference               |                              |                    |                |       | 2.0                |       | V                      |

| V <sub>REFB</sub>                     | Bottom of Reference            |                              |                    |                |       | 1.0                |       | V                      |

| V <sub>REFT</sub> - V <sub>REFB</sub> | Differential Reference Voltage |                              |                    |                |       | 1.0                |       | V                      |

|                                       | Overrange Output Code          |                              |                    | 1, 2, 3        | 16383 | 16383              |       | Code                   |

|                                       | Underrange Output Code         |                              |                    | 1, 2, 3        |       | 0                  | 0     | Code                   |

| FULL CHANN                            | EL PERFORMANCE SPECIFICAT      | TIONS                        |                    |                |       |                    |       |                        |

|                                       |                                | 5 MHz                        |                    | 1, 2, 3        | -1.03 | 0.78               | 1.53  |                        |

|                                       |                                | 5 MHz CDS                    |                    | 1, 2, 3        | -1.20 | 1.0                | 2.24  |                        |

| DNL                                   | Differential Non-Linearity     | 15 MHz                       |                    |                |       | 0.78               |       | LSB                    |

|                                       |                                | 25 MHz                       |                    |                |       | 0.78               |       |                        |

|                                       |                                | 40 MHz                       |                    | 1, 2, 3        | -1.03 | 0.78               | 1.45  |                        |

|                                       |                                | 5 MHz                        |                    | 1, 2, 3        | -5.38 | 1.7                | 4.38  |                        |

|                                       |                                | 5 MHz CDS                    |                    | 1, 2, 3        | -3.41 | 1.7                | 5.15  |                        |

| INL                                   | Integral Non-Linearity         | 15 MHz                       |                    |                |       | 1.9                |       | LSB                    |

|                                       |                                | 25 MHz                       |                    |                |       | 2.4                |       | V<br>V<br>Code<br>Code |

|                                       |                                | 40 MHz                       |                    | 1, 2, 3        | -9.9  | 6.0                | 7.34  |                        |

Submit Documentation Feedback

Copyright © 2010–2018, Texas Instruments Incorporated

# LM98640QML-SP Electrical Characteristics(1)(2) (continued)

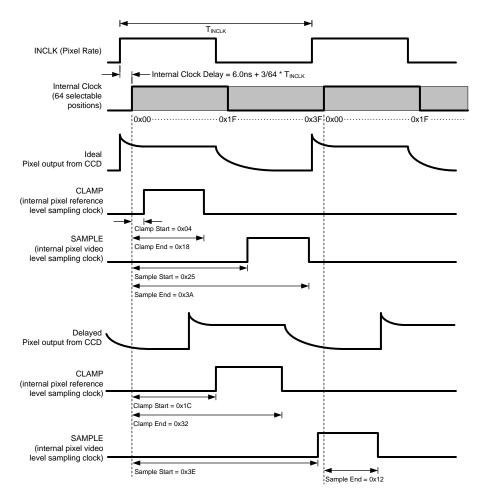

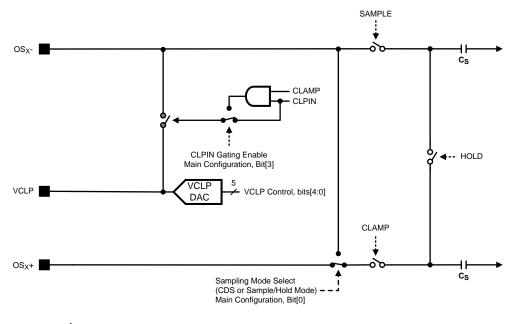

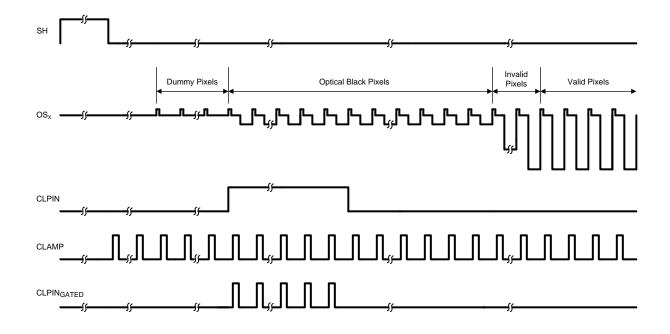

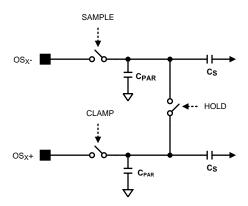

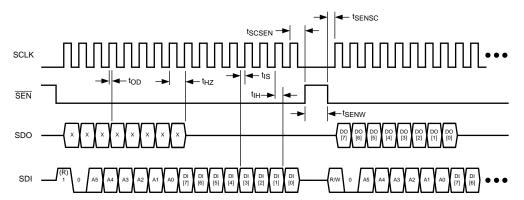

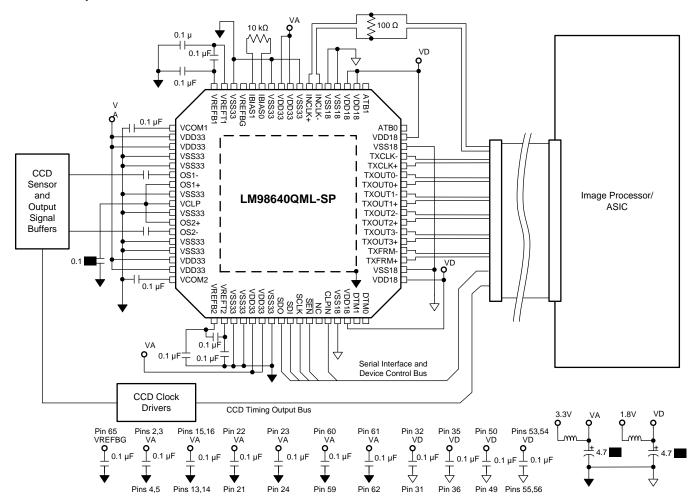

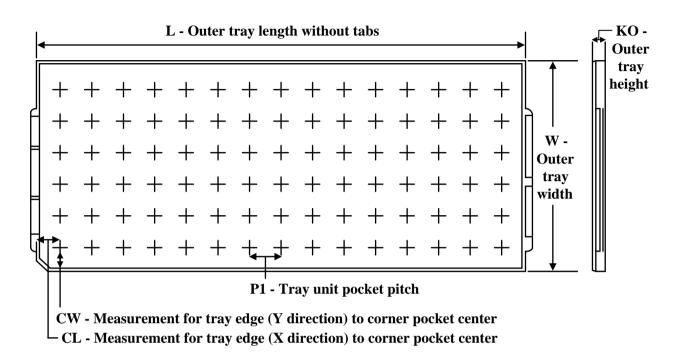

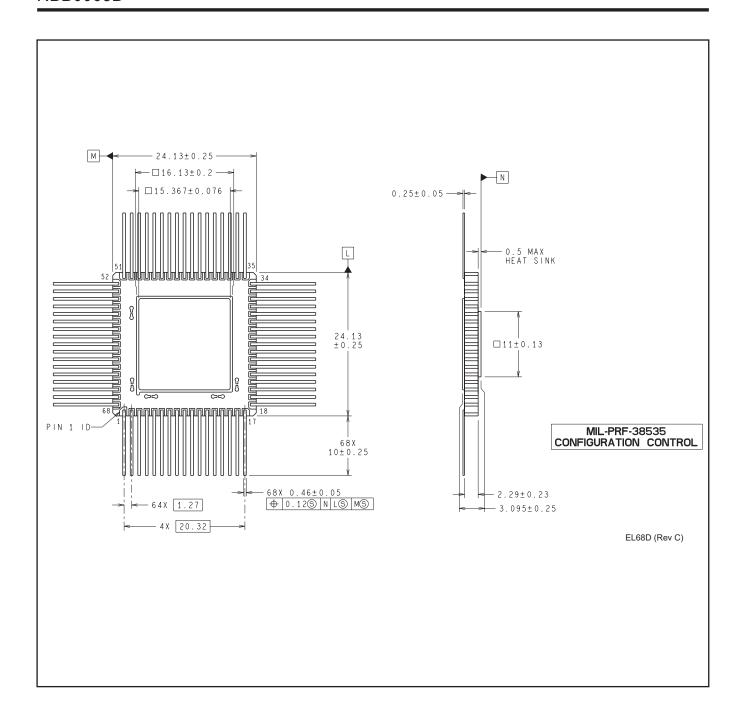

The following specifications apply for VDD33 = 3.3 V, VDD18 = 1.8 V,  $C_L$  = 10 pF, and  $f_{INCLK}$  = 40 MHz unless otherwise specified.