Sample &

Buy

### **TPA6166A2**

SLAS997B-MARCH 2014-REVISED JANUARY 2015

# TPA6166A2 3.5-mm Jack Detect and Headset Interface IC

Technical

Documents

#### 1 Features

- Ultra Low-Power, High-Performance DirectPath™ Class-G Headphone Amplifier

- Ground-Centered Output Eliminates DC-Blocking Capacitors

- 30 mW/Ch into 32  $\Omega$  / Ch at 1% THD+N

- -42 dB to +6 dB Volume Control

- 2.0 µV Output Noise at –42 dB Gain

- 91-dB PSRR

- Ground Loop Rejection for Reducing Crosstalk

- Fully Differential Mic Preamplifier With Variable Gain and 3.4-µV Low Noise

- Integrated AC-Coupling Capacitor

- Ground Loop Rejection for Reducing Headphone to Mic Crosstalk

- Choice of Two Mic Bias Voltages: 2.0 V and 2.6 V

- 92-dB PSRR

- Integrated Programmable Mic Bias Resistor

- Advanced Accessory Insertion, Removal, and Type Detection

- Passive Multi-button Support Using 10-Bit SAR ADC

- Implements Proprietary Scheme to Reduce Error Caused by Audio Playback Signal in Presence of Finite Resistance on Headset Ground Return Path

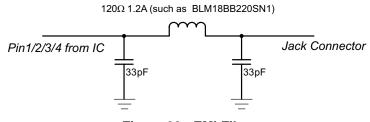

- Integrated Level-4 IEC ESD Protection on Jack Connected Pins (on EVM)

- Ultra Low-Power Chip Shutdown Mode

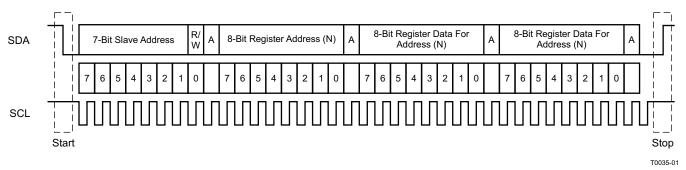

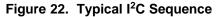

- I<sup>2</sup>C Interface

- Short-Circuit Protection

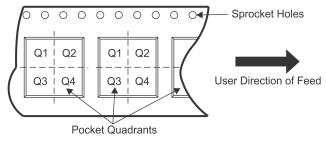

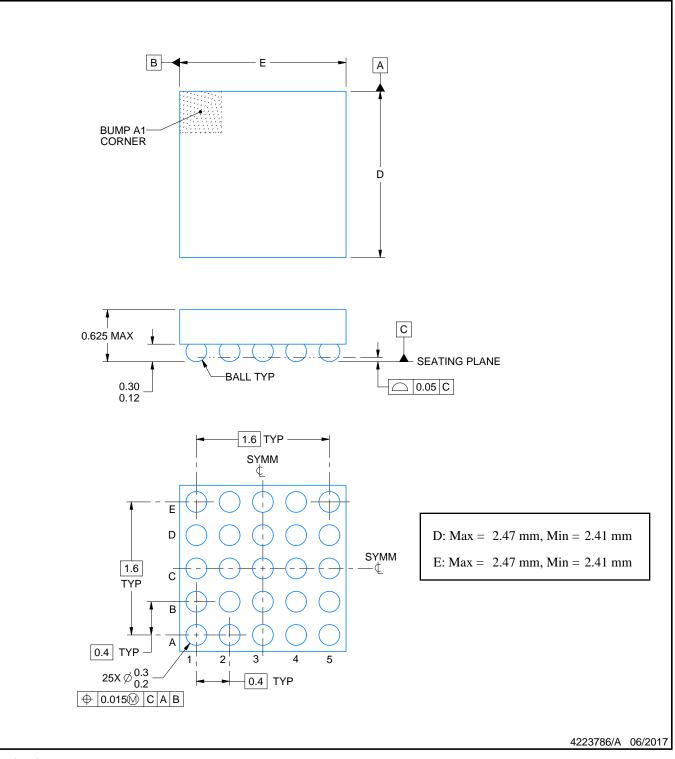

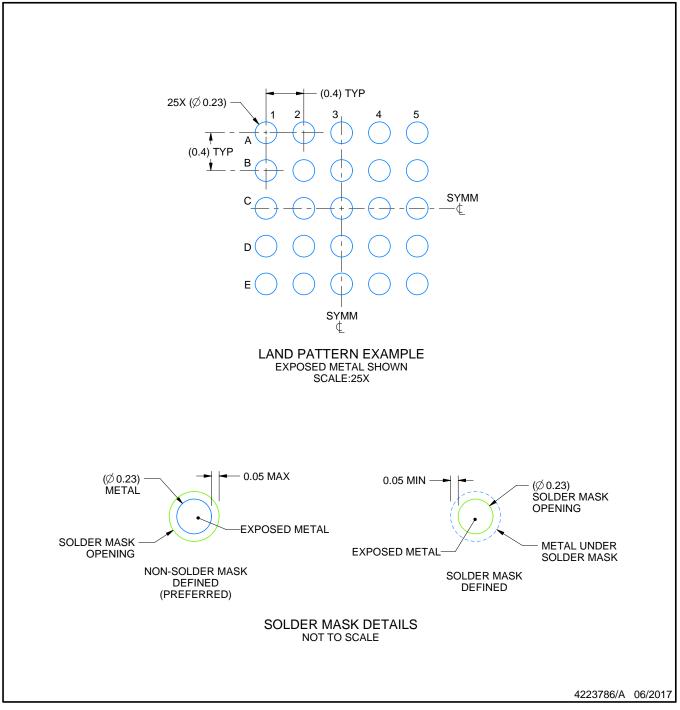

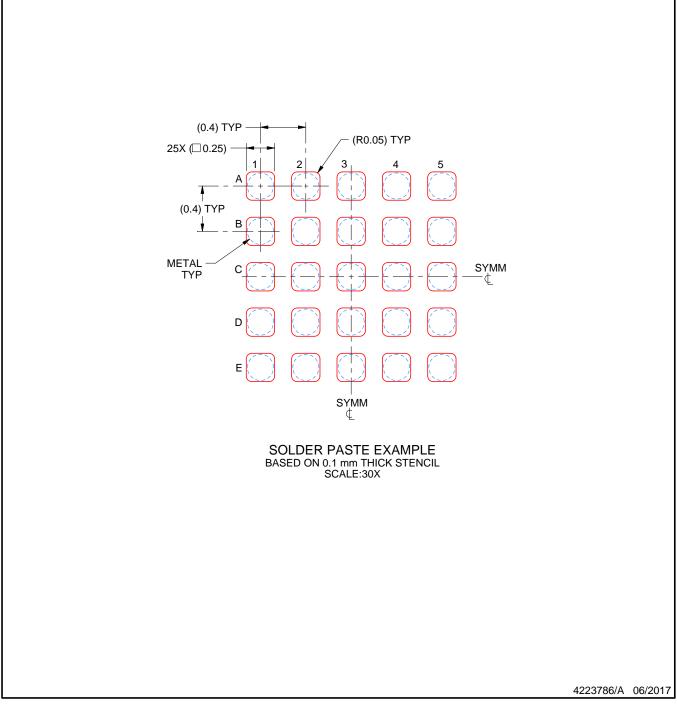

- 0.4-mm Pitch 25-Ball WCSP

#### Applications 2

- Smart Phones and Wireless Handsets

- Portable Tablets

- Notebook PCs and Docking Stations

## 3 Description

Tools &

Software

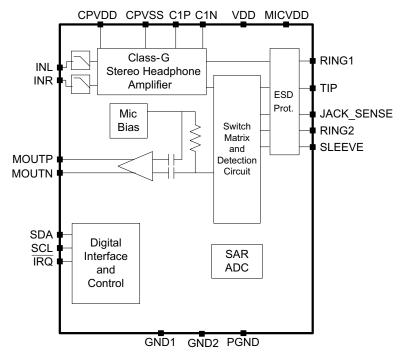

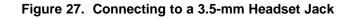

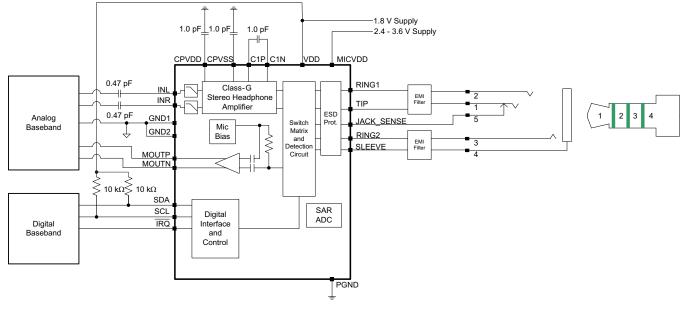

The TPA6166A2 single-chip headset interface IC simplifies the challenges of detecting what kind of device an end user has plugged into the headphone jack while delivering excellent audio quality. The device enables smaller end products by integrating a high-performance, low-power DirectPath variableattenuation class-G stereo headphone amplifier, variable-gain microphone preamplifier with bias with advanced accessory detection circuitry, all in a tiny 5-mm x 5-mm terminal, 0.4-mm pitch WCSP package.

Support &

Community

20

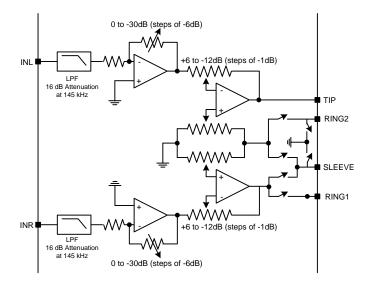

The class-G headphone amplifier maximizes battery life by adjusting the supply voltage of the headphone amplifier based on audio signal level. With 8-µV output noise at 0-dB gain and PSRR of 91 dB, the headphone amplifier provides excellent audio performance. DirectPath eliminates the need for DCblocking capacitors. The microphone preamplifier has two programmable gains of 12 dB and 24 dB, and 3.4 µV input referred noise.

The microphone bias voltage has two programmable settings of 2 V and 2.6 V. The bias output drives up to 1.2 mA of current, has a low output noise of 2  $\mu$ V, and 92-dB PSRR, providing excellent rejection of power supply noise in wireless handsets.

The advanced accessory detection algorithm automatically detects six supported accessories and enables or disables internal components.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |  |  |

|-------------|-----------|-------------------|--|--|

| TPA6166A2   | WSCP (25) | 2.50 mm × 2.50 mm |  |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

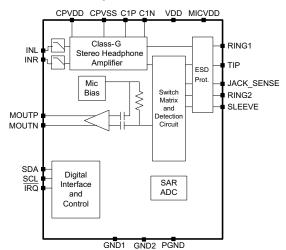

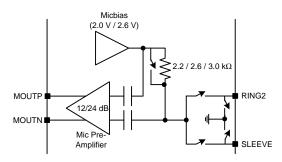

#### Simplified Schematic

# Table of Contents

| 1 | Feat | tures 1                                                 |

|---|------|---------------------------------------------------------|

| 2 | Арр  | lications 1                                             |

| 3 | Des  | cription 1                                              |

| 4 | Rev  | ision History 2                                         |

| 5 | Pin  | Configuration and Functions 3                           |

| 6 | Spe  | cifications 4                                           |

|   | 6.1  | Absolute Maximum Ratings 4                              |

|   | 6.2  | ESD Ratings 4                                           |

|   | 6.3  | Recommended Operating Conditions 4                      |

|   | 6.4  | Thermal Information 4                                   |

|   | 6.5  | Electrical Characteristics5                             |

|   | 6.6  | Electrical Characteristics, Audio Amplifiers            |

|   | 6.7  | Electrical Characteristics, Mic Preamplifier and Bias 7 |

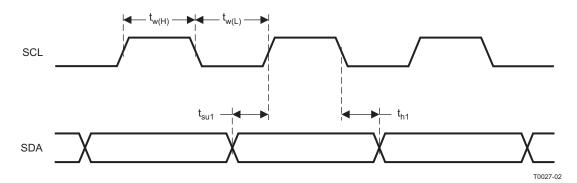

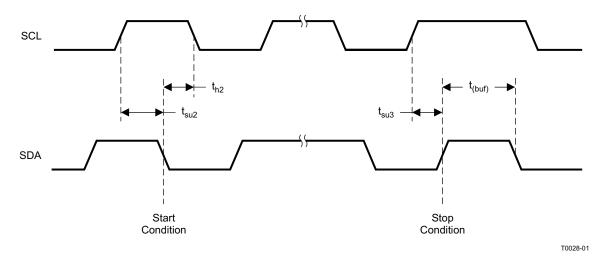

|   | 6.8  | Timing Requirements 8                                   |

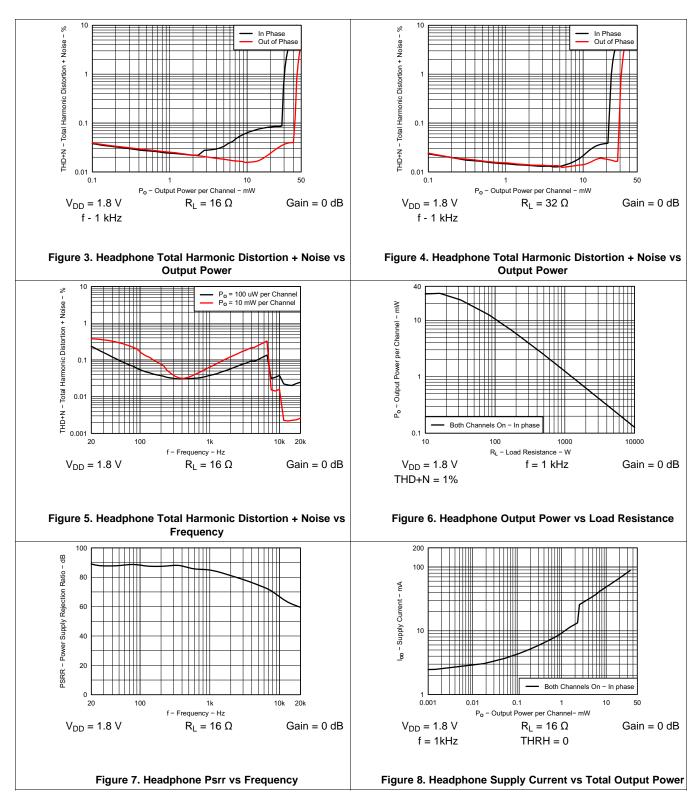

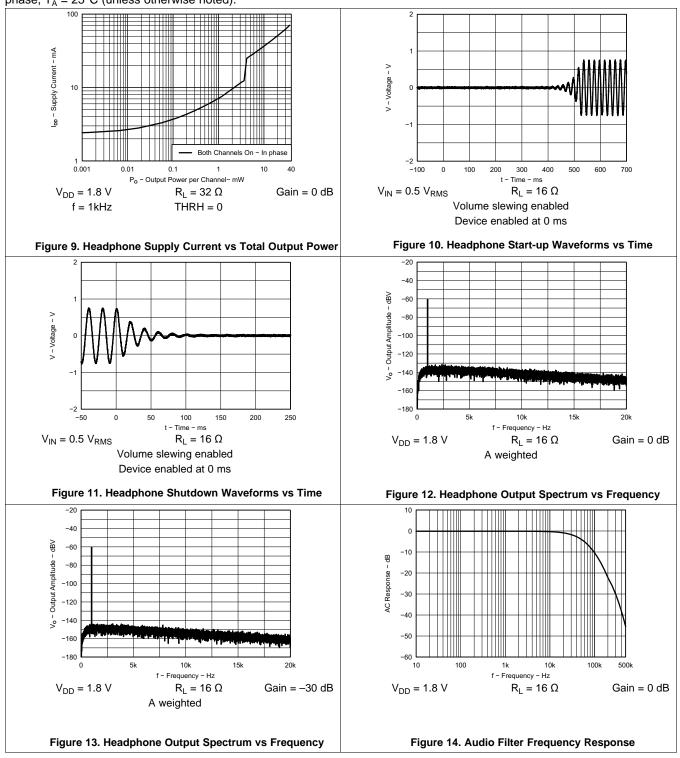

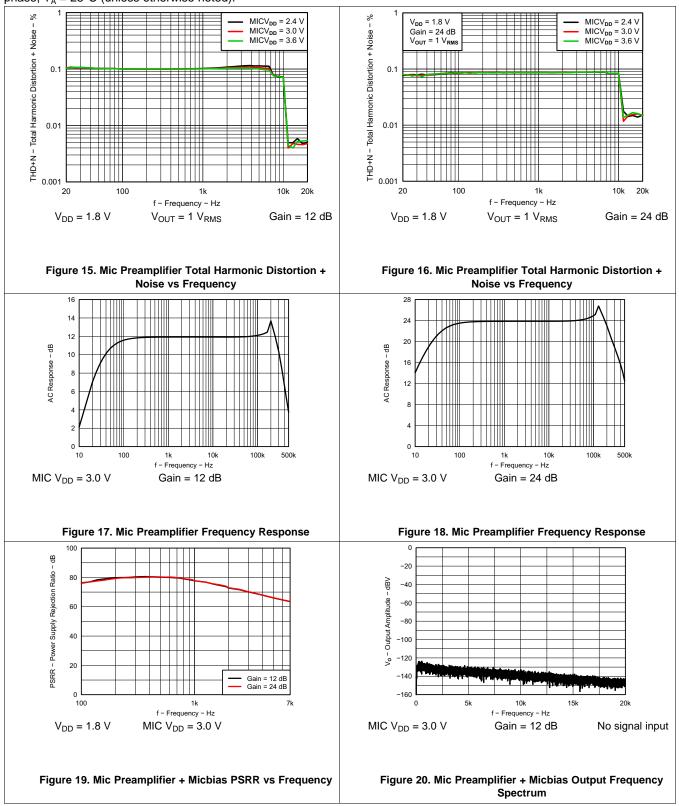

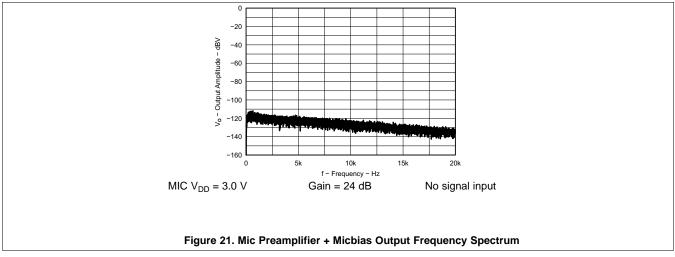

|   | 6.9  | Typical Characteristics 9                               |

| 7 | Deta | ailed Description 13                                    |

|   | 7.1  | Overview 13                                             |

|   | 7.2  | Functional Block Diagram 13                             |

|   |      |                                                         |

|    | 70   | Fasture Description               | 40 |

|----|------|-----------------------------------|----|

|    | 1.3  | Feature Description               |    |

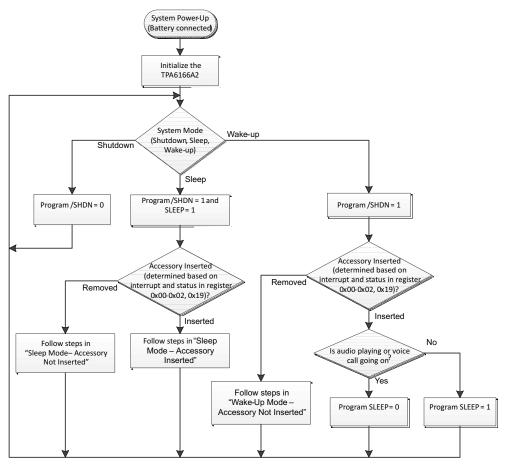

|    | 7.4  | Device Functional Modes           | 19 |

|    | 7.5  | Register Maps                     | 23 |

| 8  | App  | lication and Implementation       | 38 |

|    | 8.1  | Application Information           | 38 |

|    | 8.2  | Typical Application               | 38 |

| 9  |      | er Supply Recommendations         |    |

|    | 9.1  | Decoupling Capacitors             | 40 |

| 10 | Lay  | out                               | 41 |

|    | 10.1 | Layout Guidelines                 | 41 |

|    | 10.2 | Layout Example                    | 42 |

| 11 |      | ice and Documentation Support     |    |

|    | 11.1 | Development Support               | 43 |

|    | 11.2 | Trademarks                        | 43 |

|    | 11.3 | Electrostatic Discharge Caution   | 43 |

|    | 11.4 | Glossary                          | 43 |

| 12 | Mec  | hanical, Packaging, and Orderable |    |

|    | Info | mation                            | 43 |

## 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

### Changes from Revision A (June 2014) to Revision B

| Changes from Original (January 2014) to Revision A                                                                                                                                                                                                                                                                                           | Page   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| <ul> <li>Added Pin Configuration and Functions section, ESD Ratings table, Feature Description section, Device Fu.<br/>Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, I<br/>and Documentation Support section, and Mechanical, Packaging, and Orderable Information section</li> </ul> | Device |

| • | Changed to new data sheet format                 | 1 |

|---|--------------------------------------------------|---|

| • | Added specifications and application information | 1 |

| • | Changed status to Production Data                | 1 |

www.ti.com

Page

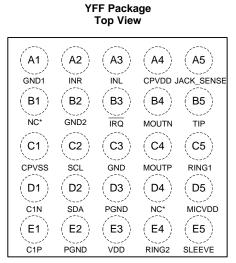

## 5 Pin Configuration and Functions

All NC pins should be left floating. Do not connect them to GND.

#### **Pin Functions**

| PIN           |        |            | DECODIDENCI                                                                                                                                 |  |  |

|---------------|--------|------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME          | NO.    | I/O / TYPE | DESCRIPTION                                                                                                                                 |  |  |

| GND1          | A1     | Р          | Analog / digital ground 1                                                                                                                   |  |  |

| INR           | A2     | I          | Headphone right channel input                                                                                                               |  |  |

| INL           | A3     | I          | Headphone left channel input                                                                                                                |  |  |

| CPVDD         | A4     | I          | Headphone charge-pump positive supply (internally generated). Connect a $1\mbox{-}\mu\mbox{F}$ capacitor to ground.                         |  |  |

| JACK_SENSE    | A5     | I/O        | Connect to headset jack terminal 5 (for mechanical switch). If mechanical switch is not available, then this terminal can be kept floating. |  |  |

| NC (Floating) | B1     | 0          | Leave floating (no connection)                                                                                                              |  |  |

| GND2          | B2     | I          | Ground 2 - Connect to ground 1 on board.                                                                                                    |  |  |

| IRQ           | B3     | 0          | Active low interrupt output                                                                                                                 |  |  |

| MOUTN         | B4     | 0          | Microphone preamplifier negative output                                                                                                     |  |  |

| TIP           | B5     | 0          | Left headphone / line output. Connect to headset jack TIP (terminal 1).                                                                     |  |  |

| CPVSS         | C1     | I          | Headphone charge-pump negative supply (internally generated). Connect a $1\mathcharge F$ capacitor to ground.                               |  |  |

| SCL           | C2     | I          | I <sup>2</sup> C clock line                                                                                                                 |  |  |

| GND           | C3     | I          | Connect to ground                                                                                                                           |  |  |

| MOUTP         | C4     | 0          | Microphone preamplifier positive output                                                                                                     |  |  |

| RING1         | C5     | 0          | Right headphone / line output. Connect to headset jack RING1 (terminal 2).                                                                  |  |  |

| C1N           | D1     | Р          | Charge pump flying capacitor positive terminal                                                                                              |  |  |

| SDA           | D2     | I/O        | I <sup>2</sup> C data line                                                                                                                  |  |  |

| PGND          | D3, E2 | Р          | Power ground                                                                                                                                |  |  |

| NC (Floating) | D4     | 0          | Leave floating (no connection)                                                                                                              |  |  |

| MICVDD        | D5     | Р          | Analog supply                                                                                                                               |  |  |

| C1P           | E1     | Р          | Charge pump flying capacitor negative terminal                                                                                              |  |  |

| VDD           | E3     | Р          | Analog / digital supply                                                                                                                     |  |  |

| RING2         | E4     | I/O        | Connect to headset jack RING2 (terminal 3)                                                                                                  |  |  |

| SLEEVE        | E5     | I/O        | Connect to headset jack SLEEVE (terminal 4)                                                                                                 |  |  |

## 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating temperature range,  $T_A = 25^{\circ}C$  (unless otherwise noted) <sup>(1)</sup>

|                                           | MIN        | MAX            | UNIT |

|-------------------------------------------|------------|----------------|------|

| Supply voltage, VDD                       | -0.3       | 2              | V    |

| Microphone supply voltage, MICVDD         | -0.3       | 3.9            | V    |

| Output continuous total power dissipation | See Therma | al Information |      |

| Storage temperature, T <sub>stg</sub>     | -65        | 85             | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                 |                              |                                                                          | VALUE | UNIT |

|-----------------|------------------------------|--------------------------------------------------------------------------|-------|------|

|                 |                              | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>        | ±2000 |      |

| V <sub>(E</sub> | ESD) Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22- $C101^{(2)}$ | ±500  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

|                    |                          |                                                                                               | MIN | MAX | UNIT |

|--------------------|--------------------------|-----------------------------------------------------------------------------------------------|-----|-----|------|

| VDD                | Supply voltage           | 1.7                                                                                           | 1.9 | V   |      |

| MICVDD             | Microphone supply        | voltage                                                                                       | 2.4 | 3.6 | V    |

| T <sub>A</sub>     | Operating temperatu      | Operating temperature                                                                         |     | 85  | °C   |

|                    |                          | Line Driver Application, $R_L$ = 10 k\Omega, $A_V \ge 0$ dB, specified by design              |     | 470 | pF   |

| C <sub>L,Max</sub> | Maximum load capacitance | Line Driver Application, R_L = 10 k\Omega, A_V \le 0 dB, LO_EXT_STAB = 1, specified by design |     | 470 |      |

|                    |                          | Headphone Application, $R_L = 32 \Omega$ , specified by design                                |     | 200 |      |

| TJ                 | Operating junction te    | Operating junction temperature                                                                |     | 150 | °C   |

## 6.4 Thermal Information

|                       |                                              | TPA6166A2  |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | YFF (WSCP) | UNIT |

|                       |                                              | 25 PINS    |      |

| $R_{	extsf{	heta}JA}$ | Junction-to-ambient thermal resistance       | 67         |      |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 18         |      |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 38         | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 0.1        |      |

| Ψ <sub>JB</sub>       | Junction-to-board characterization parameter | 36         |      |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

### 6.5 Electrical Characteristics

VDD =00 1.8 V, MICVDD = 3.0 V, A<sub>V</sub> = 0 dB, C<sub>IN</sub> = 0.47  $\mu$ F, C<sub>FLY</sub> = 1.0  $\mu$ F, C<sub>CPVDD</sub> = C<sub>CPVSS</sub> = 1.0  $\mu$ F, R<sub>HP</sub> = 32  $\Omega$ , outputs in phase, T<sub>A</sub> = 25°C (unless otherwise noted).

|                                                              | PARAMETER                            | TEST CC                                                    | NDITIONS                              | MIN     | TYP   | MAX | UNIT |

|--------------------------------------------------------------|--------------------------------------|------------------------------------------------------------|---------------------------------------|---------|-------|-----|------|

| VIH                                                          | Input logic high                     | SDA, SCL                                                   |                                       | 1.4     |       |     |      |

| V <sub>IL</sub>                                              | Input logic low                      | SDA, SCL                                                   |                                       |         |       | 0.4 | V    |

| V <sub>OL</sub>                                              | Output logic low                     | ĪRQ                                                        | I <sub>OL</sub> = 3 mA pullup current | 0.2×VDD |       |     |      |

| I <sub>IH</sub>                                              | Logic high input<br>leakage current  | SDA, SCL                                                   |                                       |         |       | 1   |      |

| I <sub>IL</sub>                                              | Logic low input<br>leakage current   | SDA, SCL                                                   |                                       |         |       | 1   | μA   |

| II <sub>OH</sub> I                                           | Logic high output<br>leakage current | ĪRQ                                                        | V <sub>IRQ</sub> = 3.3 V              |         |       | 1   |      |

| ,                                                            |                                      |                                                            | I <sub>VDD</sub>                      |         | 2.38  |     | mA   |

|                                                              |                                      | Audio playback (both channels), no signal into 32 $\Omega$ |                                       |         | 0.21  |     | mA   |

|                                                              |                                      |                                                            | P <sub>CONS</sub> <sup>(1)</sup>      |         | 4.91  |     | mW   |

|                                                              |                                      | Audio playback (both                                       | I <sub>VDD</sub>                      |         | 3.74  |     | mA   |

|                                                              |                                      | channels), 100-µW output into                              |                                       |         | 0.21  |     | mA   |

|                                                              |                                      | 32 Ω                                                       | P <sub>CONS</sub> <sup>(1)</sup>      |         | 7.35  |     | mW   |

|                                                              |                                      | 2-way call, no signal into 32 $\Omega$                     | I <sub>VDD</sub>                      |         | 2.36  |     | mA   |

|                                                              |                                      |                                                            |                                       |         | 0.96  |     | mA   |

|                                                              |                                      |                                                            | P <sub>CONS</sub> <sup>(1)</sup>      |         | 6.35  |     | mW   |

|                                                              |                                      |                                                            | I <sub>VDD</sub>                      |         | 3.68  |     | mA   |

| Power c                                                      | consumption                          | 2-way call, 100-μW output into 32 Ω                        |                                       |         | 0.96  |     | mA   |

|                                                              |                                      | 52.52                                                      | P <sub>CONS</sub> <sup>(1)</sup>      |         | 8.74  |     | mW   |

|                                                              |                                      |                                                            | I <sub>VDD</sub>                      |         | 10.84 |     | μA   |

|                                                              |                                      | Accessory not inserted                                     |                                       |         | 1.05  |     | μA   |

| Accessory not inser<br>mechanical switch i<br>(JACK_SENSE=1) |                                      |                                                            | P <sub>CONS</sub> <sup>(1)</sup>      |         | 22.7  |     | μW   |

|                                                              |                                      | Accessory not inserted.                                    | I <sub>VDD</sub>                      |         | 150.9 |     | μA   |

|                                                              |                                      | mechanical switch is open                                  | IMICVDD                               |         | 1.05  |     | μA   |

|                                                              |                                      | (JACK_SENSE=1)                                             | P <sub>CONS</sub> <sup>(1)</sup>      |         | 278.3 |     | μW   |

|                                                              |                                      |                                                            | I <sub>VDD</sub>                      |         | 108.1 |     | μA   |

|                                                              |                                      | Accessory inserted and in sleep mode                       | IMICVDD                               |         | 1.06  |     | μA   |

|                                                              |                                      | mode                                                       | P <sub>CONS</sub> <sup>(1)</sup>      |         | 197.8 |     | μW   |

(1) Total power consumption from VDD and MICVDD.

#### **TPA6166A2**

SLAS997B-MARCH 2014-REVISED JANUARY 2015

www.ti.com

## 6.6 Electrical Characteristics, Audio Amplifiers

$VDD = 1.8 \text{ V}, \text{ MICVDD} = 3.0 \text{ V}, \text{ A}_{\text{V}} = 0 \text{ dB}, \text{ C}_{\text{IN}} = 0.47 \text{ }\mu\text{F}, \text{ C}_{\text{FLY}} = 1.0 \text{ }\mu\text{F}, \text{ C}_{\text{CPVDD}} = \text{C}_{\text{CPVSS}} = 1.0 \text{ }\mu\text{F}, \text{ R}_{\text{L}} = 32 \text{ }\Omega\text{, outputs in phase, } \text{T}_{\text{A}} = 25^{\circ}\text{C} \text{ (unless otherwise noted)}.}$

|                      | PARAMETER                                                  | TEST CONDITION                                                                                                                                               | IS                            | MIN  | TYP    | MAX | UNIT              |  |

|----------------------|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|------|--------|-----|-------------------|--|

| HEADPH               | ONE AND LINE-OUT AMPLIFIERS                                |                                                                                                                                                              |                               |      |        |     |                   |  |

|                      | Programmable gain range                                    |                                                                                                                                                              |                               | -42  |        | 6   | dB                |  |

| A <sub>V,Max</sub>   |                                                            | $A_V = 6 \text{ dB}$                                                                                                                                         |                               | 5.0  | 6.0    | 7.0 | dB                |  |

| A <sub>V,Min</sub>   |                                                            | $A_V = -42 \text{ dB}$                                                                                                                                       |                               | -43  | -42    | -41 | dB                |  |

|                      | Gain step size                                             | -42 dB $\leq A_V \leq 6$ dB                                                                                                                                  |                               |      | 1      |     | dB                |  |

| $\Delta A_V$         | Gain matching                                              | Between left and right channels                                                                                                                              |                               | -0.5 |        | 0.5 | dB                |  |

|                      | Mute attenuation                                           |                                                                                                                                                              |                               |      | 103.7  |     | dB                |  |

|                      |                                                            | THD+N = 1%, f = 1 kHz, $R_L = 32$ channel on                                                                                                                 | Ω, single                     |      | 29.1   |     |                   |  |

|                      |                                                            | THD+N = 1%, f = 1 kHz, $R_L$ = 32<br>C both channels on                                                                                                      | Ω,                            |      | 23.2   |     |                   |  |

| Po                   | Output power                                               | THD+N = 1%, f = 1 kHz, $R_L = 16$ channel on                                                                                                                 | Ω, single                     |      | 43.0   |     | mW                |  |

|                      |                                                            | THD+N = 1%, f = 1 kHz, $R_L$ = 16<br>processing of Request 596221 wa<br>10:19 on 28 Jan 2015. Click here<br>data Click here to access the HTM<br>channels on | as completed at to access the |      | 30.2   |     |                   |  |

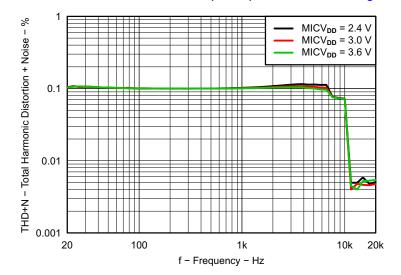

|                      | Total harmonic distortion plus noise                       | $R_{L} = 16 \Omega, P_{O} = 10 \text{ mW}, \text{ f} = 1 \text{ kHz}$                                                                                        |                               |      | 0.021% |     |                   |  |

| THD+N                |                                                            | $R_{L} = 16 \Omega, P_{O} = 0.1 \text{ mW}, \text{ f} = 1 \text{ kHz}$                                                                                       |                               |      | 0.057% |     | l                 |  |

|                      | 10136                                                      | $R_L$ = 10 kΩ, $V_{OUT}$ = 1 $V_{RMS}$ , f = 1 kHz                                                                                                           |                               |      | 0.014% |     | l                 |  |

|                      | Power supply rejection ratio                               | $f = dc, VDD = 1.7 V to 1.9 V, A_V = 0 dB$                                                                                                                   |                               | 70   | 91     |     |                   |  |

| PSRR                 |                                                            | f = 217 Hz, 100 mV <sub>P-P</sub> ripple on VDD                                                                                                              |                               |      | 88     |     | dB                |  |

|                      |                                                            | f = 10 kHz, 100 mV <sub>P-P</sub> ripple on VDD                                                                                                              |                               |      | 71     |     |                   |  |

|                      |                                                            | $A_V = 0 \text{ dB}$                                                                                                                                         |                               |      | 8.0    |     |                   |  |

| E <sub>N</sub>       | Output noise <sup>(1)</sup>                                | A <sub>V</sub> = -30 dB                                                                                                                                      |                               |      | 2.0    |     | μV <sub>RMS</sub> |  |

|                      |                                                            | A <sub>V</sub> = -42 dB                                                                                                                                      |                               |      | 2.0    |     | l                 |  |

|                      | Crosstalk between left and right                           | $R_{L} = 16 \ \Omega, f = 1 \ \text{kHz}, P_{O} = 5 \ \text{mW}$<br>$R_{L} = 32 \ \Omega, f = 1 \ \text{kHz}, P_{O} = 25 \ \text{mW}$                        |                               |      | -56    |     | ٩D                |  |

|                      | channels                                                   |                                                                                                                                                              |                               |      | -62    |     | dB                |  |

| R <sub>IN</sub>      | Amplifier input resistance                                 |                                                                                                                                                              |                               |      | 20     |     | kΩ                |  |

| V <sub>OOS</sub>     | Output offset voltage                                      | $A_V = 0 \text{ dB}$                                                                                                                                         |                               | -0.5 |        | 0.5 | mV                |  |

| V <sub>OUT,Max</sub> | Max line output voltage                                    | $R_L = 10 \ k\Omega$                                                                                                                                         |                               |      | 1      |     | V <sub>RMS</sub>  |  |

| f <sub>C,LPF</sub>   | Input low-pass filter 3-dB cutoff frequency <sup>(2)</sup> | $A_V = 0 \text{ dB}$                                                                                                                                         |                               |      | 45.1   |     | kHz               |  |

|                      | Low-pass filter passband gain <sup>(2)</sup>               | f = 10 Hz to 15 kHz, dc-coupled in $V_{CM} = 0 V$                                                                                                            | nputs with                    |      | -0.4   |     | dB                |  |

|                      | Low-pass filter stopband gain <sup>(2)</sup>               | f = 145 kHz                                                                                                                                                  |                               |      | -16    |     | dB                |  |

| f <sub>CP</sub>      | Charge pump frequency                                      |                                                                                                                                                              |                               |      | 1.3    |     | MHz               |  |

|                      | Click and pop <sup>(1)</sup>                               | $A_V = 0 \text{ dB}$ , Volume Slewing                                                                                                                        | Into shutdown                 |      | -83    |     | l                 |  |

|                      |                                                            | Enabled, $R_L = 32 \Omega$ , peak voltage, 32 samples / second                                                                                               | Out of shutdown               |      | -69    |     | dBV               |  |

|                      |                                                            | $P_O = 0.5 \text{ mW}, R_L = 32 \Omega$                                                                                                                      |                               |      | 6.2    |     |                   |  |

|                      | Power consumption <sup>(3)</sup>                           | $P_{O} = 5 \text{ mW}, R_{L} = 32 \Omega, \text{THRH} = 2$                                                                                                   | 1                             |      | 13.3   |     | mW                |  |

|                      |                                                            | $P_0 = 30 \text{ mW}, R_L = 32 \Omega, THRH = 0$                                                                                                             |                               |      | 56.9   |     | I                 |  |

| RL                   | Minimum headphone load                                     |                                                                                                                                                              |                               |      | 32     | 7.8 | Ω                 |  |

A-weighted

Measured with respect to gain at 997 Hz

(3) Per output channel

## 6.7 Electrical Characteristics, Mic Preamplifier and Bias

VDD = 1.8 V, MICVDD = 3.0 V,  $T_A = 25^{\circ}C$  (unless otherwise noted).

|                   | PARAMETER                                         | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                     |             | TYP        | MAX   | UNIT              |  |

|-------------------|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------------|------------|-------|-------------------|--|

| MICROP            | HONE BIAS                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                     |             |            |       |                   |  |

|                   | Missenhaue bies weltere                           | Programmed for high value, MICVDD $\geq$ 2.8 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                     |             | 2.6        | 2.75  | v                 |  |

| V <sub>BIAS</sub> | Microphone bias voltage                           | Programmed for low value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1.88                                                                                                                                | 2.0         | 2.12       | v     |                   |  |

| I <sub>OUT</sub>  | Max bias output current                           | Internal bias resistor bypassed (M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ICR = 011)                                                                                                                          |             | 1.2        |       | mA                |  |

|                   |                                                   | MICR = 000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | MICR = 000                                                                                                                          |             |            | 2.31  |                   |  |

| Р                 |                                                   | MICR = 001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                     | 2.47        | 2.6        | 2.73  | kΩ                |  |

| R <sub>BIAS</sub> | Bias output resistance                            | MICR = 010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                     | 2.85        | 3.0        | 3.15  |                   |  |

|                   |                                                   | MICR = 011                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                     |             | 0.13       |       |                   |  |

| E <sub>N</sub>    | Bias output noise <sup>(1)</sup>                  | Between SLEEVE and RING2, BV 2.2 k $\Omega$ load between SLEEVE and V <sub>BIAS</sub> = 2.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                     |             | 2.0        |       | μV <sub>RMS</sub> |  |

| PSRR Power supply |                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | f = dc,<br>MICVDD = 2.8 V to<br>3.6 V                                                                                               |             | 92         |       |                   |  |

|                   | Power supply rejection ratio                      | Measured between SLEEVE and RING2, 2.2 k $\Omega$ load between SLEEVE and RING2, MODE and RING2, MO | f = 2 kHz, 100 mV <sub>P-P</sub><br>ripple,<br>MICVDD = 3.0 V                                                                       |             | 73         |       | dB                |  |

|                   |                                                   | MICR = 000, V <sub>BIAS</sub> = 2.6 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | f = 2 kHz, 100 mV <sub>P-P</sub><br>ripple,<br>MICVDD = 2.8 V                                                                       |             | 73         |       |                   |  |

| MicZ              | Microphone Capsule Impedance                      | Measured between Mic and GND before insertion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                     | 1500        |            | 20000 | Ω                 |  |

| MICROP            | HONE PREAMPLIFIER                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                     |             |            |       |                   |  |

|                   |                                                   | Programmed for high value, f = 997 Hz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                     |             | 24         | 25    |                   |  |

| A <sub>V</sub>    | Preamplifier gain                                 | Programmed for low value, f = 997 Hz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                     |             | 12         | 13    | dB                |  |