March 2010

# FDMC6675BZ

# P-Channel Power Trench<sup>®</sup> MOSFET -30 V, -20 A, 14.4 m $\Omega$

### **Features**

- Max  $r_{DS(on)}$  = 14.4 m $\Omega$  at  $V_{GS}$  = -10 V,  $I_D$  = -9.5 A

- Max  $r_{DS(on)}$  = 27.0 m $\Omega$  at  $V_{GS}$  = -4.5 V,  $I_D$  = -6.9 A

- HBM ESD protection level of 8 kV typical(note 3)

- Extended V<sub>GSS</sub> range (-25 V) for battery applications

- High performance trench technology for extremely low r<sub>DS(on)</sub>

- High power and current handling capability

- Termination is Lead-free and RoHS Compliant

The FDMC6675BZ has been designed to minimize losses in load switch applications. Advancements in both silicon and package technologies have been combined to offer the lowest  $r_{\text{DS}(\text{on})}$  and ESD protection.

### **Application**

- Load Switch in Notebook and Server

- Notebook Battery Pack Power Management

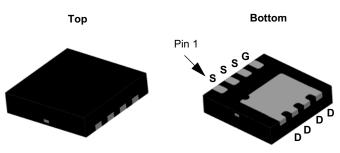

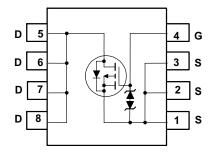

MLP 3.3x3.3

### MOSFET Maximum Ratings TA = 25 °C unless otherwise noted

| Symbol                            | Parameter                                    | Parameter              |           |             | Units |

|-----------------------------------|----------------------------------------------|------------------------|-----------|-------------|-------|

| $V_{DS}$                          | Drain to Source Voltage                      |                        |           | -30         | V     |

| $V_{GS}$                          | Gate to Source Voltage                       |                        |           | ±25         | V     |

|                                   | Drain Current -Continuous (Package limited)  | T <sub>C</sub> = 25 °C |           | -20         |       |

|                                   | -Continuous (Silicon limited)                | T <sub>C</sub> = 25 °C |           | -40         | ^     |

| ID                                | -Continuous                                  | T <sub>A</sub> = 25 °C | (Note 1a) | -9.5        | A     |

|                                   | -Pulsed                                      |                        |           | -32         |       |

| Б                                 | Power Dissipation                            | T <sub>C</sub> = 25 °C |           | 36          | 10/   |

| $P_{D}$                           | Power Dissipation                            | T <sub>A</sub> = 25 °C | (Note 1a) | 2.3         | W     |

| T <sub>J</sub> , T <sub>STG</sub> | Operating and Storage Junction Temperature R | ange                   |           | -55 to +150 | °C    |

### **Thermal Characteristics**

| $R_{\theta JC}$   | Thermal Resistance, Junction to Case       |          | 3.4 | °C/M |

|-------------------|--------------------------------------------|----------|-----|------|

| R <sub>e,IA</sub> | Thermal Resistance, Junction to Ambient (N | Note 1a) | 53  | °C/W |

### **Package Marking and Ordering Information**

| Device Marking | Device     | Package     | Reel Size | Tape Width | Quantity   |

|----------------|------------|-------------|-----------|------------|------------|

| FDMC6675BZ     | FDMC6675BZ | MLP 3.3X3.3 | 13 "      | 12 mm      | 3000 units |

# **Electrical Characteristics** $T_J = 25$ °C unless otherwise noted

| Symbol                               | Parameter                                    | Test Conditions                                                                  | Min | Тур | Max        | Units |

|--------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------|-----|-----|------------|-------|

| Off Chara                            | ncteristics                                  |                                                                                  |     |     |            |       |

| BV <sub>DSS</sub>                    | Drain to Source Breakdown Voltage            | I <sub>D</sub> = -250 μA, V <sub>GS</sub> = 0 V                                  | -30 |     |            | V     |

| $\frac{\Delta BV_{DSS}}{\Delta T_J}$ | Breakdown Voltage Temperature<br>Coefficient | I <sub>D</sub> = -250 μA, referenced to 25 °C                                    |     | 20  |            | mV/°C |

| I <sub>DSS</sub>                     | Zero Gate Voltage Drain Current              | $V_{DS} = -24 \text{ V},$<br>$V_{GS} = 0 \text{ V}$ $T_{\perp} = 125 \text{ °C}$ |     |     | -1<br>-100 | μА    |

| I <sub>GSS</sub>                     | Gate to Source Leakage Current               | $V_{GS} = \pm 25 \text{ V}, V_{DS} = 0 \text{ V}$                                |     |     | ±10        | μА    |

### **On Characteristics**

Symbol

| V <sub>GS(th)</sub>                    | Gate to Source Threshold Voltage                            | $V_{GS} = V_{DS}, I_D = -250 \mu A$                                        | -1.0 | -1.9 | -3.0 | V     |

|----------------------------------------|-------------------------------------------------------------|----------------------------------------------------------------------------|------|------|------|-------|

| $\frac{\Delta V_{GS(th)}}{\Delta T_J}$ | Gate to Source Threshold Voltage<br>Temperature Coefficient | $I_D$ = -250 μA, referenced to 25 °C                                       |      | -6   |      | mV/°C |

|                                        |                                                             | $V_{GS} = -10 \text{ V}, I_D = -9.5 \text{ A}$                             |      | 10.7 | 14.4 |       |

| r <sub>DS(on)</sub>                    | r <sub>DS(on)</sub> Static Drain to Source On Resistance    | $V_{GS} = -4.5 \text{ V}, I_D = -6.9 \text{ A}$                            |      | 17.4 | 27.0 | mΩ    |

|                                        |                                                             | $V_{GS} = -10 \text{ V}, I_D = -9.5 \text{ A}, T_J = 125 ^{\circ}\text{C}$ |      | 15.2 | 20.5 |       |

| 9 <sub>FS</sub>                        | Forward Transconductance                                    | $V_{DD} = -5 \text{ V}, \ I_{D} = -9.5 \text{ A}$                          |      | 28   |      | S     |

### **Dynamic Characteristics**

| C <sub>iss</sub> | Input Capacitance            | V - 45 V V - 0 V                                             | 2154 | 2865 | pF |

|------------------|------------------------------|--------------------------------------------------------------|------|------|----|

| C <sub>oss</sub> | Output Capacitance           | V <sub>DS</sub> = -15 V, V <sub>GS</sub> = 0 V,<br>f = 1 MHz | 392  | 525  | pF |

| C <sub>rss</sub> | Reverse Transfer Capacitance | 1 - 1 101112                                                 | 349  | 525  | pF |

### **Switching Characteristics**

| t <sub>d(on)</sub>  | Turn-On Delay Time            |                                              |                                                                              |  | 11  | 20 | ns |

|---------------------|-------------------------------|----------------------------------------------|------------------------------------------------------------------------------|--|-----|----|----|

| t <sub>r</sub>      | Rise Time                     | V <sub>DD</sub> = -15 V, I <sub>D</sub> = -9 | $V_{DD}$ = -15 V, $I_{D}$ = -9.5 A, $V_{GS}$ = -10 V, $R_{GEN}$ = 6 $\Omega$ |  | 10  | 20 | ns |

| t <sub>d(off)</sub> | Turn-Off Delay Time           | $V_{GS}$ = -10 V, $R_{GEN}$                  |                                                                              |  | 44  | 71 | ns |

| t <sub>f</sub>      | Fall Time                     |                                              |                                                                              |  | 26  | 42 | ns |

| 0                   | Total Gate Charge             | V <sub>GS</sub> = 0 V to -10 V               |                                                                              |  | 46  | 65 | nC |

| $Q_{g(TOT)}$        | Total Gate Charge             | $V_{GS} = 0 \text{ V to } -5 \text{ V}$      | V <sub>DD</sub> = -15 V,                                                     |  | 26  | 37 | nC |

| Q <sub>gs</sub>     | Gate to Source Charge         |                                              | I <sub>D</sub> = -9.5 A                                                      |  | 6.4 |    | nC |

| $Q_{gd}$            | Gate to Drain "Miller" Charge |                                              |                                                                              |  | 13  |    | nC |

### **Drain-Source Diode Characteristics**

| V <sub>SD</sub> Source to Drain Diode Forward Voltage | $V_{GS} = 0 \text{ V}, I_S = -9.5 \text{ A}$ (Note 2) |                                                       | 0.89 | 1.3  | V   |    |

|-------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|------|------|-----|----|

| $V_{SD}$                                              | Source to Drain blode Forward voltage                 | $V_{GS} = 0 \text{ V}, I_S = -1.6 \text{ A}$ (Note 2) |      | 0.73 | 1.2 | V  |

| t <sub>rr</sub>                                       | Reverse Recovery Time                                 | $I_F = -9.5 \text{ A, di/dt} = 100 \text{ A/µs}$ 24   |      | 24   | 38  | ns |

| Q <sub>rr</sub>                                       | Reverse Recovery Charge                               |                                                       |      | 15   | 27  | nC |

<sup>1.</sup> R<sub>0JA</sub> is determined with the device mounted on a 1 in<sup>2</sup> pad 2 oz copper pad on a 1.5 x 1.5 in. board of FR-4 material. R<sub>0JC</sub> is guaranteed by design while R<sub>0CA</sub> is determined by the user's board design.

a. 53 °C/W when mounted on a 1 in<sup>2</sup> pad of 2 oz copper

b.125 °C/W when mounted on a minimum pad of 2 oz copper

- 2. Pulse Test: Pulse Width < 300  $\mu s,$  Duty cycle < 2.0 %.

- 3. The diode connected between the gate and source servers only as protection against ESD. No gate overvoltage rating is implied.

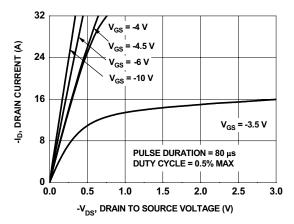

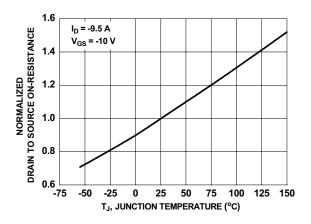

### Typical Characteristics T<sub>J</sub> = 25 °C unless otherwise noted

Figure 1. On Region Characteristics

Figure 3. Normalized On Resistance vs Junction Temperature

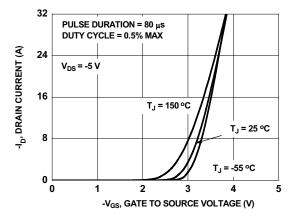

Figure 5. Transfer Characteristics

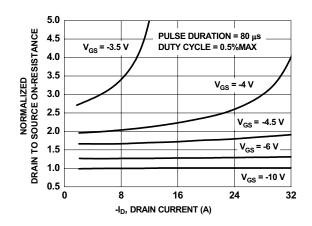

Figure 2. Normalized On-Resistance vs Drain Current and Gate Voltage

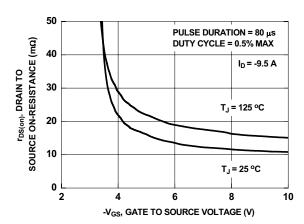

Figure 4. On-Resistance vs Gate to Source Voltage

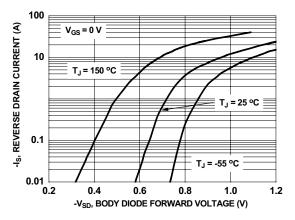

Figure 6. Source to Drain Diode Forward Voltage vs Source Current

# Typical Characteristics $T_J = 25$ °C unless otherwise noted

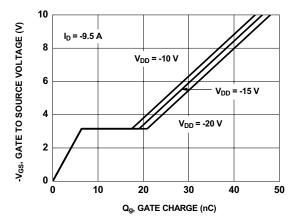

Figure 7. Gate Charge Characteristics

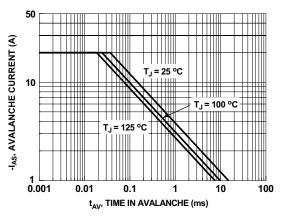

Figure 9. Unclamped Inductive Switching Capability

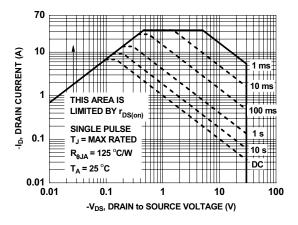

Figure 11. Forward Bias Safe Operating Area

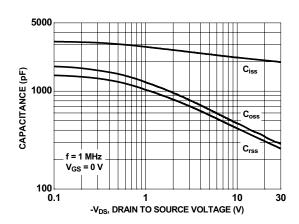

Figure 8. Capacitance vs Drain to Source Voltage

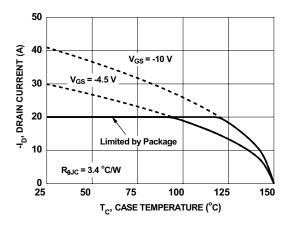

Figure 10. Maximum Continuous Drain Current vs Case Temperature

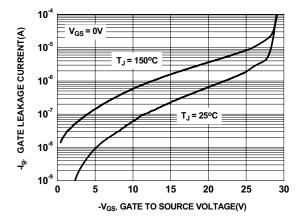

Figure 12. I<sub>qss</sub> vs V<sub>qss</sub>

# **Typical Characteristics** T<sub>J</sub> = 25 °C unless otherwise noted

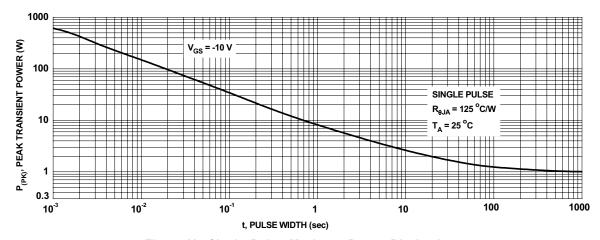

Figure 13. Single Pulse Maximum Power Dissipation

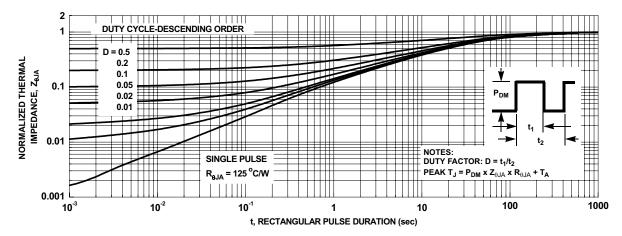

Figure 14. Junction-to-Ambient Transient Thermal Response Curve

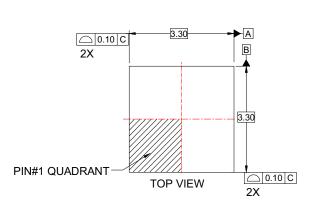

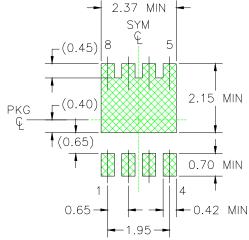

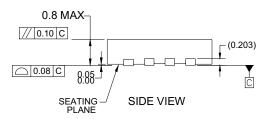

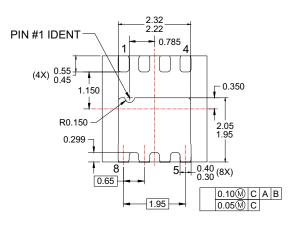

## **Dimensional Outline and Pad Layout**

RECOMMENDED LAND PATTERN

**BOTTOM VIEW**

### NOTES:

- A. DOES NOT CONFORM TO JEDEC REGISTRATION MO-229

- B. DIMENSIONS ARE IN MILLIMETERS.

- C. DIMENSIONS AND TOLERANCES PER ASME Y14.5M, 1994

- D. DRAWING FILE NAME: MLP08SREVA

- E. LAND PATTERN RECOMMENDATION IS BASED ON FSC DESIGN ONLY

### **TRADEMARKS**

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks.

AccuPower™ Auto-SPM™ Build it Now™ CorePLUS™ CorePOWER™  $CROSSVOLT^{\text{TM}}$ CTL™ Current Transfer Logic™ DEUXPEED® Dual Cool™ EcoSPARK® EfficentMax™

Fairchild<sup>®</sup>

Fairchild Semiconductor® FACT Quiet Series™ **FACT**  $\tilde{\mathsf{FAST}^{\mathbb{R}}}$ FastvCore™

FETBench™ FlashWriter® \* FPS™ F-PFS™

FRFET® Global Power Resource<sup>SM</sup>

Green FPS™ Green FPS™ e-Series™

Gmax™ GTO™ IntelliMAX™ ISOPLANAR™ MegaBuck™ MICROCOUPLER™

MicroFET™ MicroPak™ MicroPak2™ MillerDrive™ MotionMax™ Motion-SPM™ OptiHiT™ OPTOLOGIC® OPTOPLANAR®

PDP SPM™ Power-SPM™ PowerTrench® PowerXS™

Programmable Active Droop™

**OFET®** QS<sup>TM</sup> Quiet Series™ RapidConfigure<sup>™</sup>

Saving our world, 1mW/W/kW at a time™ SignalWise™

SmartMax™ SMART START™ SPM<sup>®</sup> STEALTH™ SuperFET™

SuperSOT™-3 SuperSOT™-6 SuperSOT™-8 SupreMOS™ SyncFET™ Sync-Lock™

SYSTEM®\*

The Power Franchise® bwer franchise TinyBoost™ TinyBuck™ TinyCalc™ TinyLogic<sup>®</sup> TINYOPTO™ TinyPower™ TinyPWM™ TinyWire™ TriFault Detect™ TRUECURRENT™\*

**UHC**® Ultra FRFET™ UniFET™ VCX™ VisualMax™ XS™

μSerDes™

\*Trademarks of System General Corporation, used under license by Fairchild Semiconductor.

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- 2. A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

### **ANTI-COUNTERFEITING POLICY**

Fairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, www.Fairchildsemi.com, under Sales Support.

Counterfeiting of semiconductor parts is a growing problem in the industry. All manufactures of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed application, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handing and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address and warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

### PRODUCT STATUS DEFINITIONS **Definition of Terms**

| Datasheet Identification                  | Product Status | Definition                                                                                                                                                                                          |

|-------------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance Information Formative / In Design |                | Datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                       |

| Preliminary First Production              |                | Datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |

| No Identification Needed Full Production  |                | Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design.                                               |

| Obsolete Not In Production                |                | Datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor. The datasheet is for reference information only.                                                    |

Rev 147